# FT61EC2

# **Data Sheet**

# **Key Features**

8-bit EEPROM based RISC MCU

Program: 2k x 14; RAM: 128 x 8; Data: 256 x 8

6/8/10/14/16 Pins

True 10-bit ADC accuracy ADC

7 Timers, 4 Individual PWMs - 1 with Deadband

2 Comparators, 2 Regulator outputs

Low Standby, WDT and Operation Current

POR, LVR, LVD

High ESD, High EFT

Low V<sub>DD</sub> Operation

#### 8-bit CPU (EEPROM)

• 37 RISC instructions: 2T or 4T • 16 MHz / 2T  $(V_{DD} \ge 2.7)$

• Up to 16 pins

#### **Memory**

PROGRAM: 2k x 14 bit (R/W Protect)

DATA: 256 x 8 bitRAM: 128 x 8 bit

• 8-level Hardware Stack

#### Operation Conditions (5V, 25°C)

V<sub>DD</sub> (V<sub>POR</sub> ≤ 2.0V) V<sub>POR</sub> − 5.5 V

(Self-regulated by POR, ≤1.7V for above 0°C)

• Operation Temperature Grade <sup>-40 - +85 °C</sup>

Low Standby 0.8 μA

WDT 3.2 μA

Normal Mode (16 MHz)

207 μA/mips

## **High Reliability**

• 100k cycles, >20 years / 85°C storage (typical)

• ESD > 4 kV, EFT > 5.5 kV

#### ADC (10-bit)

• True 10-bit Accuracy (≤ 1 MHz ADC clk)

• 7 + 1 Channels

V<sub>ADC-REF</sub>

✓ Internal: 2.0, 3.0, V<sub>DD</sub> ✓ External: VREF pin

· Special event trigger and Interrupt

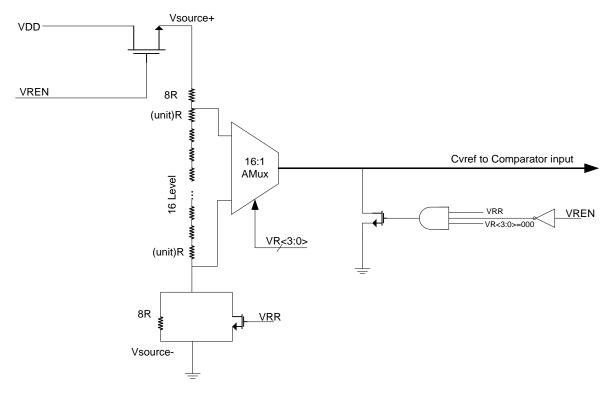

#### **2 Comparators**

• 16 level programmable voltage reference

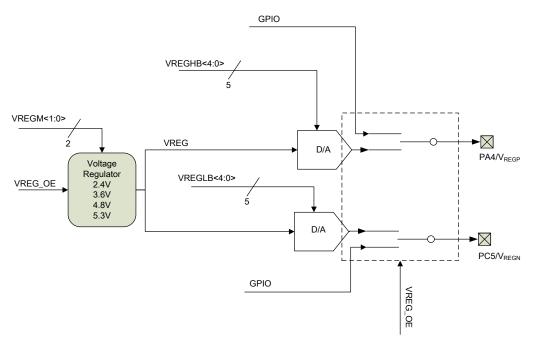

#### 2 Regulator outputs

up to 32 stalls voltage

#### PWM (Total 5)

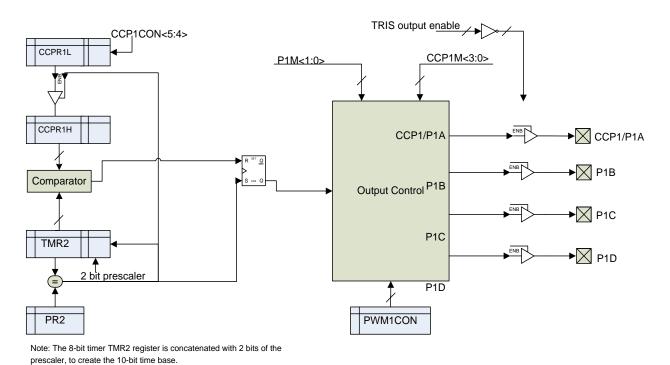

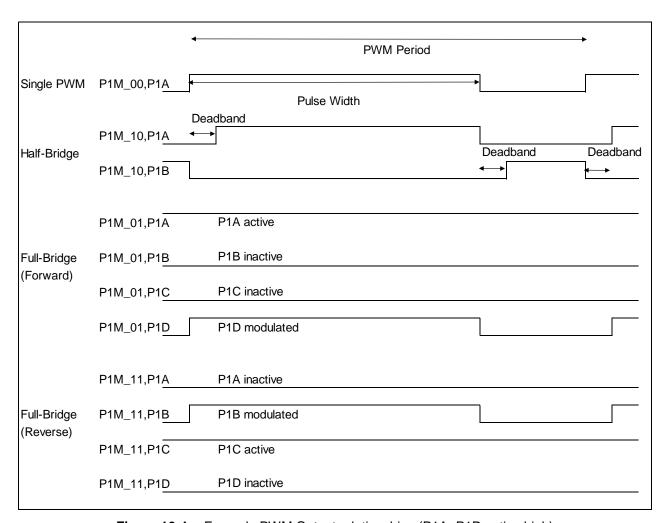

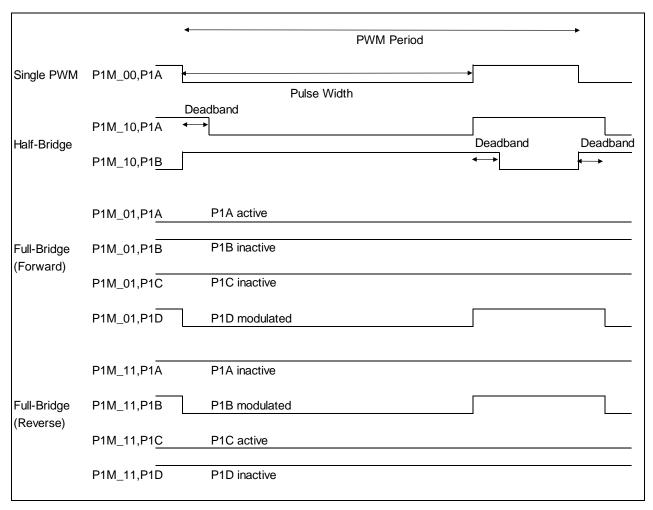

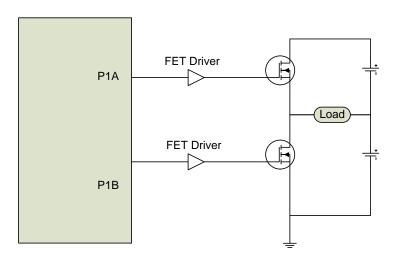

Enhanced capture/Compare/PWM

✓ PWM mode:

> single PWM, half-bridge, full-bridge

√ 3 channels (up to 6 I/O):

Complementary + Deadband

✓ One-Pulse mode

✓ Same Period, Duty Cycle

✓ Optional output polarity

PWM (3 channels)

✓ Support RUN in SLEEP

✓ Independent:Period, Duty Cycle, Polarity

√ Buzzer mode

#### **Timers**

WDT (16-bit): 7-bit postscaler

Timer0 (8-bit): 8-bit prescaler

Timer1 (16-bit): 3-bit prescaler with Gate Control

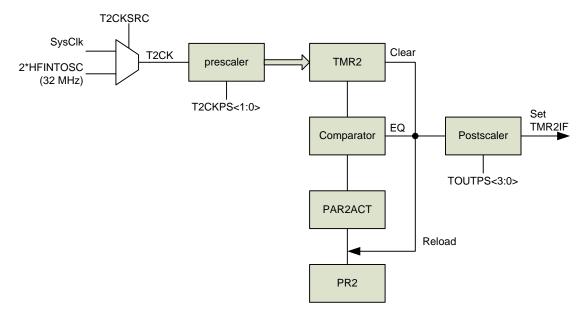

• Timer2 (8-bit): 4-bit pre and post-scaler

Timer3/4/5(12-bit): 7-bit prescaler and 8-bit postscaler

Support RUN in SLEEP

• 1 or 2x { Instr. Clock, HIRC}, LP, T0CK,T1CK

#### I/O PORTS (Up to 14 I/O)

• Resistive Pull-Up / Pull-Down

All I/O I<sub>SOURCE</sub>: 22mA (5V, 25°C)

All I/O I<sub>SINK</sub>: 19mA (5V, 25°C)

8 I/O: Interrupt / Wake-Up

#### **Power Management**

• SLEEP

• LVR: 2.0, 2.2, 2.5, 2.8, 3.1, 3.6, 4.1 (V)

• LVD: 2.0, 2.4, 2.8, 3.0, 3.6, 4.0 (V)

#### System Clock (SysClk)

✓ HIRC High Speed Internal Oscillator

√ 16MHz <±1.5% typical (2.5-5.5V, 25°C)

</p>

✓ 1, 2, 4, 8, 16, 32, 64 divider

• LIRC Low Power Internal Oscillator

✓ 32 kHz or 256 kHz

• External Clock (I/O input)

Crystal Input (LP / XT)

✓ HIRC or LIRC during startup

✓ Fail Detect

#### **Integrated Development Environment (IDE)**

On-Chip Debug (OCD), ISP

• 3 hardware breakpoints

• System-Reset, Stop, Single Step, Run

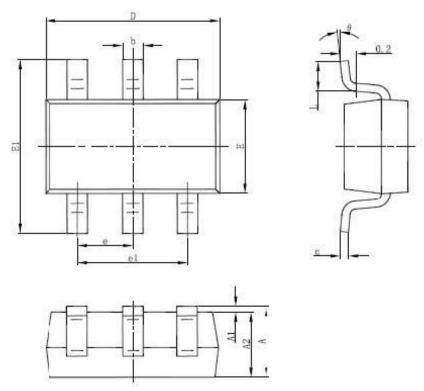

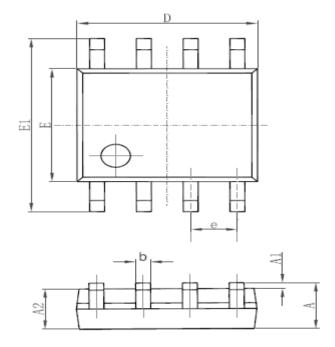

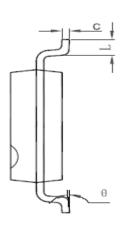

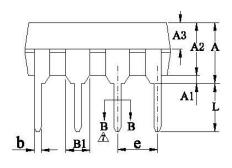

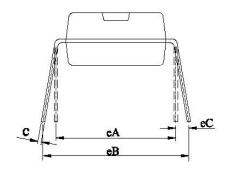

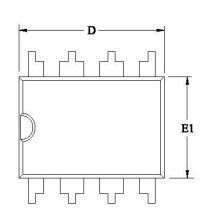

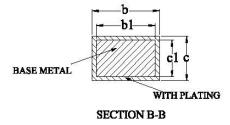

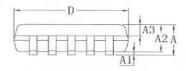

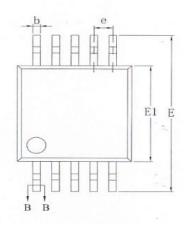

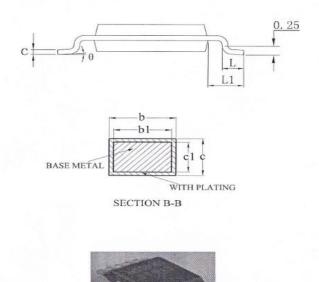

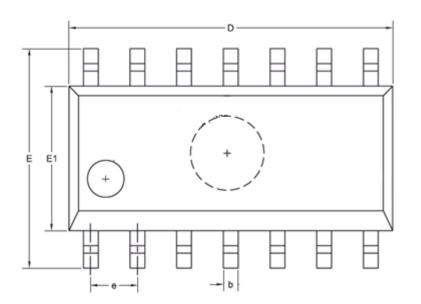

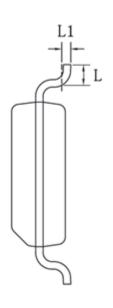

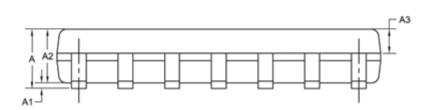

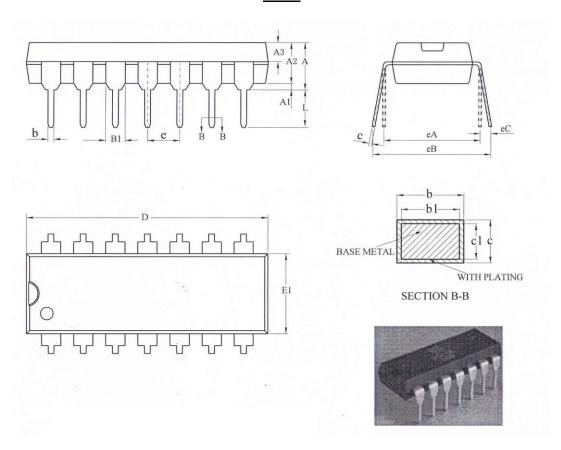

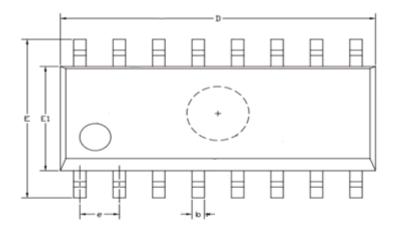

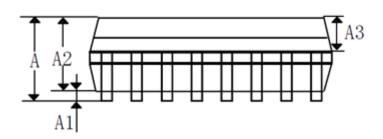

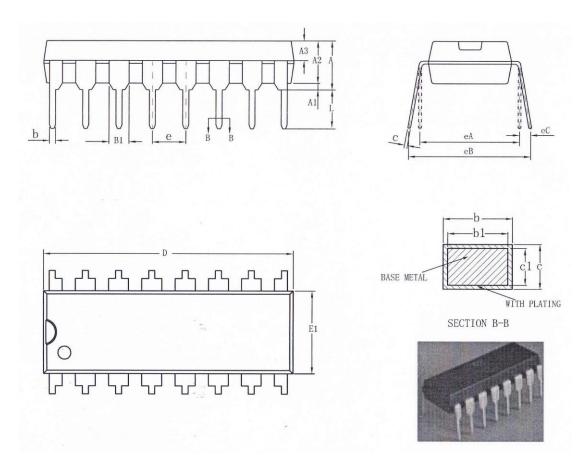

#### **Packages**

SOT23-6 SOP8 DIP8 MSOP10 SOP14 DIP14 SOP16 DIP16

Rev1.03 - 1 - 2025-03-28

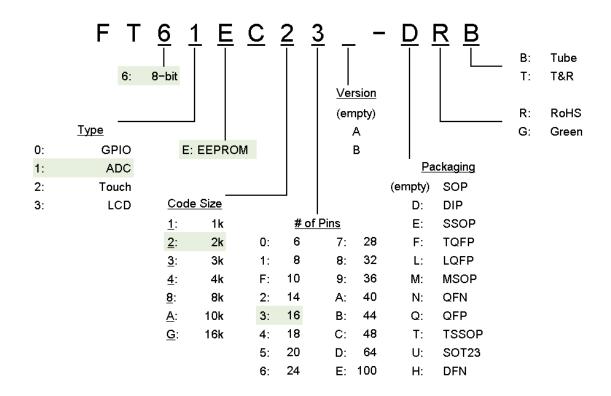

#### PARTS INFORMATION AND SELECTIONS

| Part #               | # of I/O | Package |  |  |

|----------------------|----------|---------|--|--|

| FT61EC20-Uab         | 4        | SOT23-6 |  |  |

| FT61EC21A-ab         |          | SOP8    |  |  |

| FT61EC21A-Dab        | 6        | DIP8    |  |  |

| FT61EC21B-ab         | 0        | SOP8    |  |  |

| FT61EC21B-Dab        |          | DIP8    |  |  |

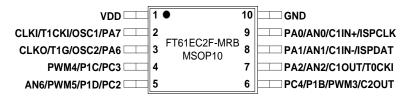

| FT61EC2F-M <u>ab</u> | 8        | MSOP10  |  |  |

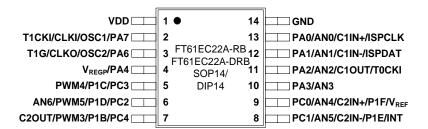

| FT61EC22A-ab         | 12       | SOP14   |  |  |

| FT61EC22A-Dab        | 12       | DIP14   |  |  |

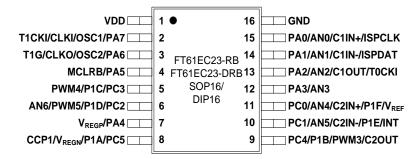

| FT61EC23- <u>ab</u>  | 14       | SOP16   |  |  |

| FT61EC23-Dab         | 14       | DIP16   |  |  |

Where

$$\underline{a} = R$$

; RoHS  $\underline{b} = B$ ; Tube  $= G$ ; Green  $= T$ ; TR

MCU Part # Selections

Rev1.03 - 2 - 2025-03-28

# **Revision History**

| Date       | Revision | Description                                                                                                                        |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 2022-08-24 | 1.00     | Preliminary version                                                                                                                |

| 2022-09-21 | 1.01     | Typo correction                                                                                                                    |

| 2024-10-29 | 1.02     | Update SOP16 packaging infromation; Typo correction                                                                                |

| 2025-03-28 | 1.03     | Update Section 6 Oscillator and Sysclk description and Figure 6-1; Update SOT23-6 and SOP14 packaging information; Typo correction |

Rev1.03 - 3 - 2025-03-28

# **Contents**

| 1. | BLOC   | K DIAGRA    | AM AND PINOUTS                            | 8  |

|----|--------|-------------|-------------------------------------------|----|

|    | 1.1    | Pinouts     |                                           | 9  |

|    | 1.2    | Pin Desc    | cription by Functions                     | 10 |

| 2. | I/O PC | ORTS        |                                           | 12 |

|    | 2.1    | Summar      | y of I/O PORT Related Registers           | 14 |

|    | 2.2    | Configuri   | ing the I/O                               | 14 |

| 3. | POWI   | ER-ON-RE    | ESET (POR)                                | 16 |

|    | 3.1    | BOOT Se     | equence                                   | 16 |

| 4. | SYST   | EM-RESE     | T                                         | 18 |

|    | 4.1    | Summar      | y of SYSTEM-RESET Related Registers       | 19 |

|    | 4.2    | Brown-O     | ut Reset (LVR / BOR)                      | 19 |

|    | 4.3    | Illegal Ins | struction Reset                           | 20 |

|    | 4.4    | Watch D     | og Timer, WDT Reset                       | 20 |

|    | 4.5    | External    | System-Reset /MCLRB                       | 20 |

|    | 4.6    | Detecting   | g the Type of Reset Last                  | 21 |

| 5. | LOW    | VOLTAGE     | DETECT / COMPARATOR (LVD)                 | 22 |

|    | 5.1    | Summar      | y of LVD Related Registers                | 22 |

| 6. | OSCII  | LLATORS     | and SYSCLK                                | 23 |

|    | 6.1    | Summar      | y of Oscillator Modules Related Registers | 24 |

|    | 6.2    | Internal (  | Clock Modes (HIRC and LIRC)               | 26 |

|    | 6.3    | External    | Clock Modes (EC / LP / XT)                | 27 |

|    |        | 6.3.1       | EC mode                                   | 27 |

|    |        | 6.3.2       | LP and XT modes                           | 27 |

|    | 6.4    | HIRC, LI    | RC and EC inter-switching                 | 29 |

| 7. | TIME   | RS and PV   | VMx                                       | 30 |

|    | 7.1    | Watch D     | og Timer, WDT                             | 31 |

|    |        | 7.1.1       | Summary of WDT Related Registers          | 32 |

|    |        | 7.1.2       | Setting up and using the WDT              | 33 |

|    |        | 7.1.3       | Switching scaler between Timer0 and WDT   | 33 |

|    | 7.2    | TIMER0.     |                                           | 34 |

|    |        | 7.2.1       | Summary of Timer0 Related Registers       | 35 |

|    |        |             |                                           |    |

|     | 7.3   | TIMER1.   |                                          | 36 |

|-----|-------|-----------|------------------------------------------|----|

|     |       | 7.3.1     | Summary of Timer1 Related Registers      | 37 |

|     |       | 7.3.2     | R/W operation of Timer1 register         | 38 |

|     |       | 7.3.3     | Timer1 Gate                              | 38 |

|     | 7.4   | TIMER2    |                                          | 39 |

|     |       | 7.4.1     | Summary of Timer2 Related Registers      | 40 |

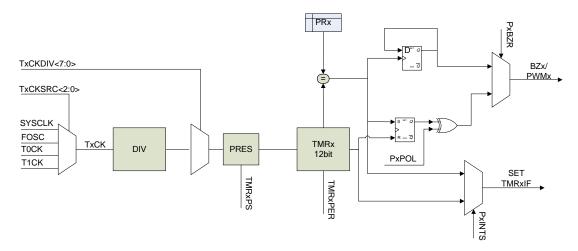

|     | 7.5   | TIMER3    | /4/5 and PWM3/4/5                        | 41 |

|     |       | 7.5.1     | Summary of Timer3/4/5b Related Registers | 42 |

|     |       | 7.5.2     | R/W operation of Timer3/4/5 register     | 44 |

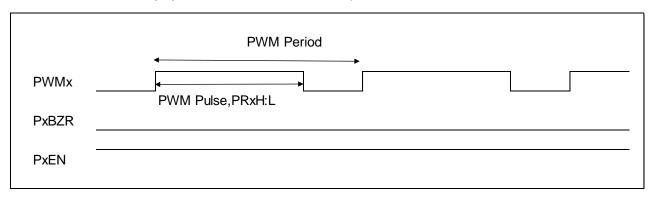

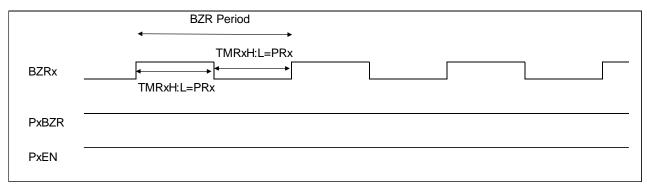

|     |       | 7.5.3     | PWMx Mode                                | 44 |

| 8.  | SLEE  | P (POWE   | R-DOWN)                                  | 46 |

|     | 8.1   | Entering  | into SLEEP                               | 46 |

|     | 8.2   | Waking-   | Up from SLEEP                            | 47 |

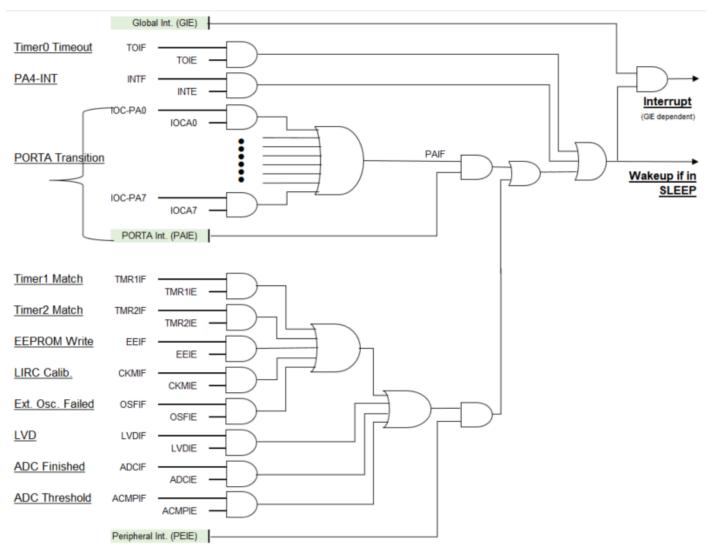

| 9.  | INTER | RRUPTS.   |                                          | 48 |

|     | 9.1   | Summar    | y of Interrupt Related Registers         | 50 |

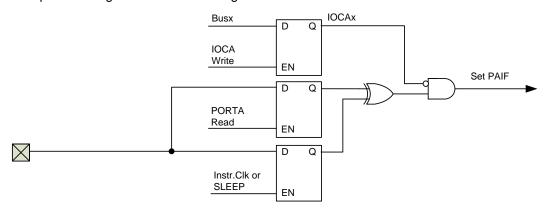

|     | 9.2   | PC1-INT   | and PORTA Interrupt-on-Change            | 52 |

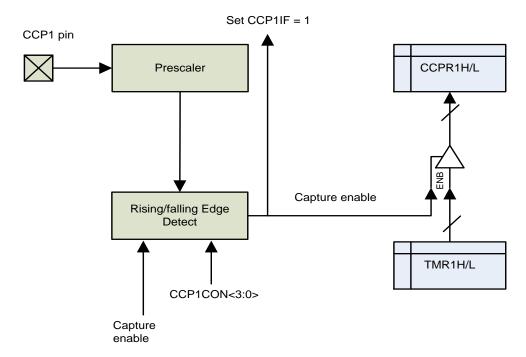

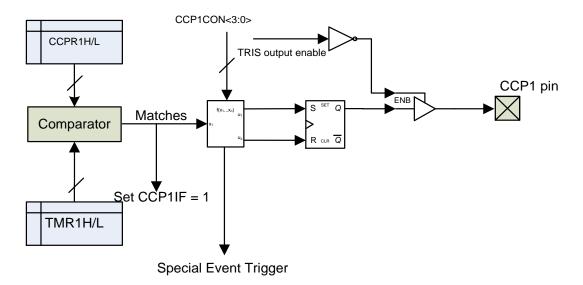

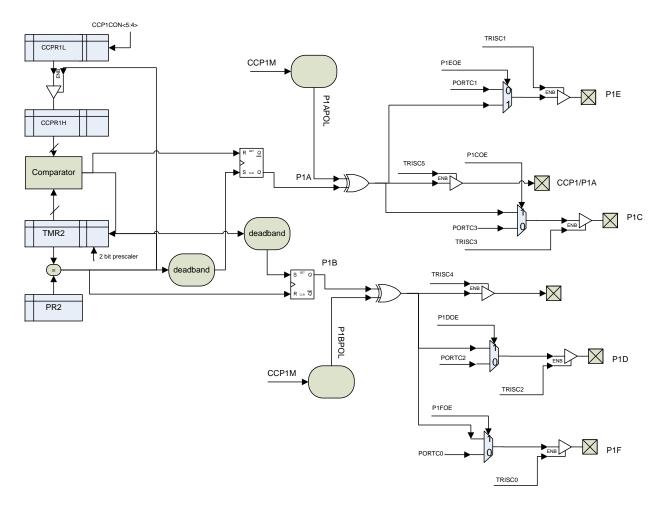

| 10. | Enhar | nced Capt | ure /Compare/PWM Module                  | 53 |

|     | 10.1  | Summar    | y of ECCP Related Registers              | 53 |

|     | 10.2  | Capture   | Mode                                     | 57 |

|     | 10.3  | Compare   | e Mode                                   | 58 |

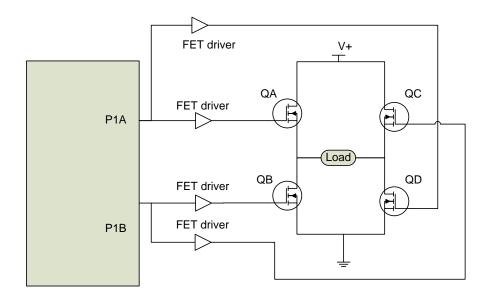

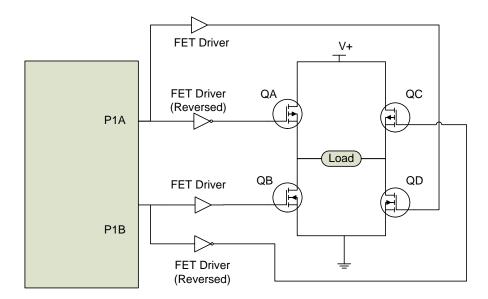

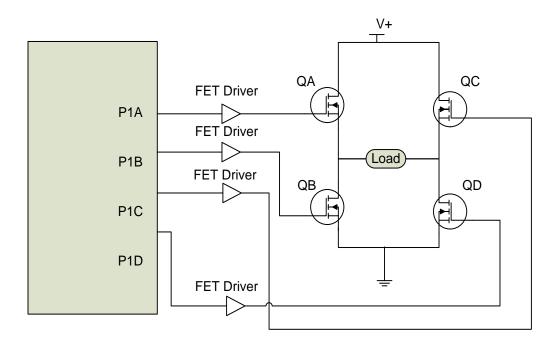

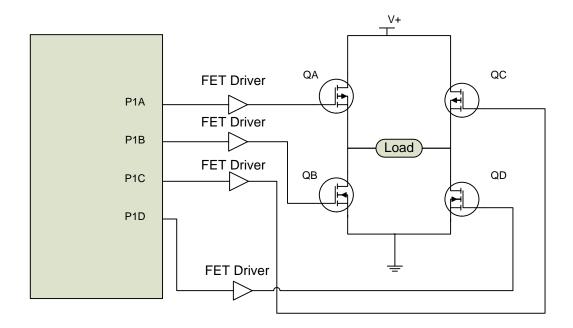

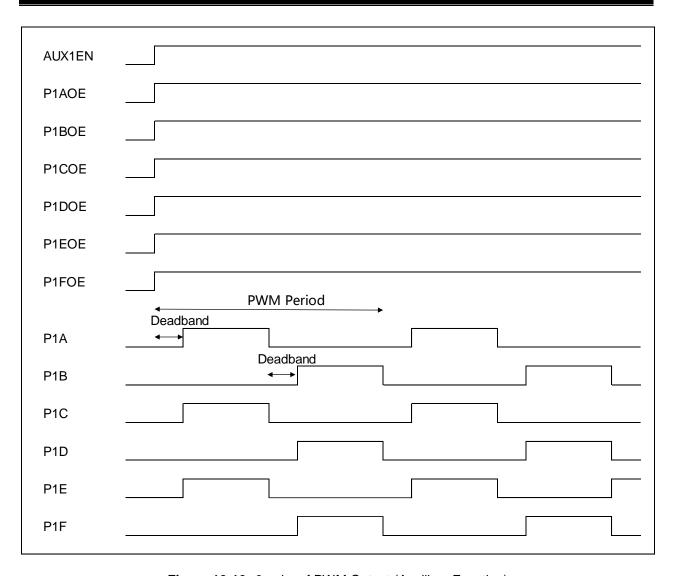

|     | 10.4  | PWM En    | hanced Mode                              | 59 |

|     |       | 10.4.1    | Period                                   | 59 |

|     |       | 10.4.2    | Duty Cycle                               | 60 |

|     |       | 10.4.3    | PWM Output                               | 60 |

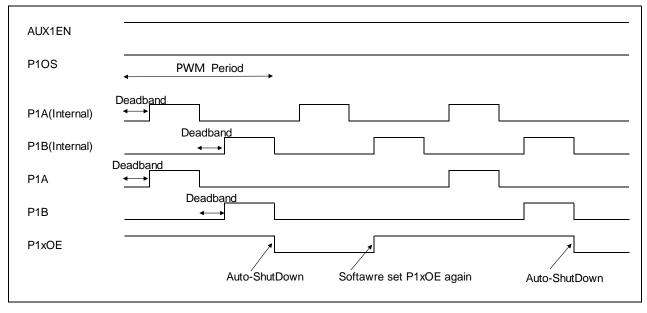

|     |       | 10.4.4    | PWM Auto-Shutdown and Auto-Restart       | 65 |

|     |       | 10.4.5    | PWM Auxiliary Function                   | 67 |

|     |       | 10.4.6    | PWM Configure Procedure                  | 69 |

| 11. | DATA  | EEPROM    | ٨                                        | 70 |

|     | 11.1  | Summar    | y of DROM Related Registers              | 70 |

|     | 11.2  | Writing E | DROM                                     | 71 |

|     | 11.3  | Reading   | DROM                                     | 72 |

|     | 11.4  | Auto-Era  | se Function                              | 72 |

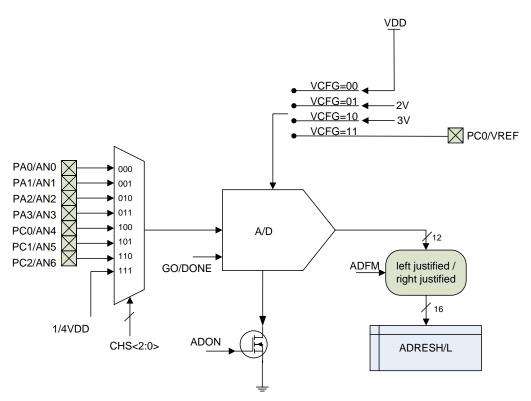

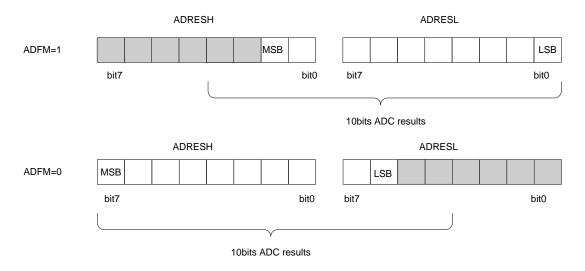

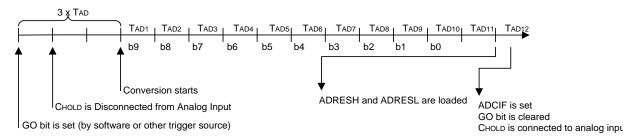

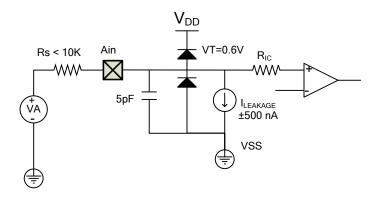

| 12. | 10-bit | ANALOG      | TO DIGITAL CONVERTER, ADC                 | 73  |

|-----|--------|-------------|-------------------------------------------|-----|

|     | 12.1   | Summar      | ry of ADC Related Registers               | 74  |

|     | 12.1   | ADC Cor     | nfigurations                              | 75  |

|     |        | 12.1.1      | ADC triggering                            | 76  |

|     |        | 12.1.2      | Aborting an ADC                           | 76  |

|     |        | 12.1.3      | Interrupt                                 | 77  |

|     | 12.2   | ADC Acc     | quisition Time                            | 77  |

|     | 12.3   | ADC Min     | nimum Sampling Time                       | 77  |

|     | 12.4   | Sample /    | ADC Flow                                  | 78  |

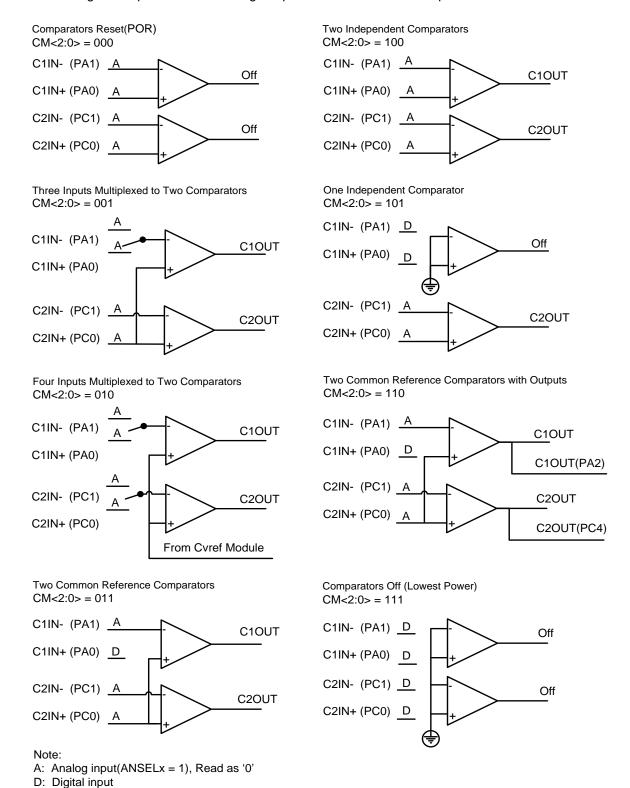

| 13. | COMF   | PARATOR     | ₹                                         | 80  |

|     | 13.1   | Summar      | ry of Comparator Related Registers        | 80  |

|     | 13.2   | Compara     | ator Configuration                        | 82  |

|     |        | 13.2.1      | Comparator Interrupt                      | 84  |

|     |        | 13.2.2      | Comparator 2 Gating Timer1                | 84  |

| 14. | VOLT   | AGE REG     | GULATOR(VREG)                             | 85  |

|     | 14.1   | Summar      | ry of Voltage Regulator Related Registers | 85  |

| 15. | MEMO   | DRY REAL    | D / PROGRAM PROTECTON                     | 86  |

| 16. | INSTR  | RUCTION     | SET                                       | 87  |

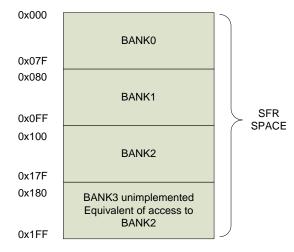

| 17. | SPEC   | IAL FUNC    | CTION REGISTERS, SFR                      | 88  |

|     | 17.1   | Boot Lev    | vel Registers                             | 88  |

|     | 17.2   | Instruction | on Set Registers                          | 90  |

|     | 17.3   | STATUS      | S Register                                | 94  |

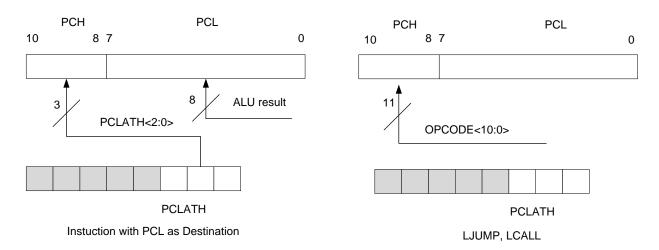

|     | 17.4   | PCL and     | PCLATH                                    | 95  |

| 18. | ELEC   | TRICAL S    | SPECIFICATIONS                            | 96  |

|     | 18.1   | Absolute    | Maximum Ratings                           | 96  |

|     | 18.2   | Operatio    | on Characteristics                        | 96  |

|     | 18.3   | POR, LV     | /R, LVD                                   | 97  |

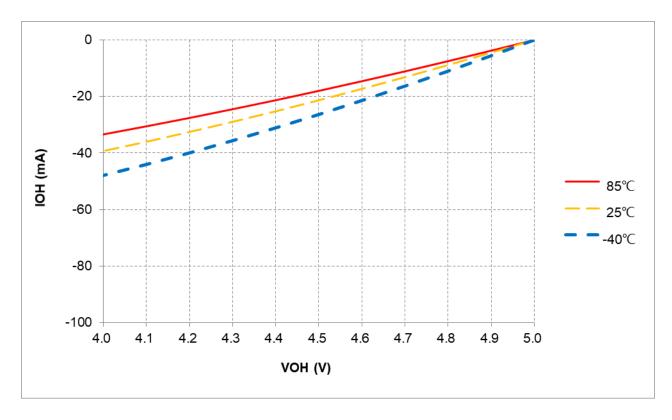

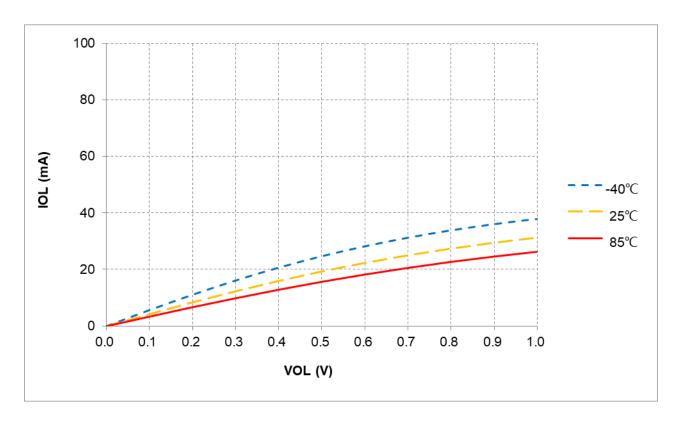

|     | 18.4   | I/O POR     | TS                                        | 98  |

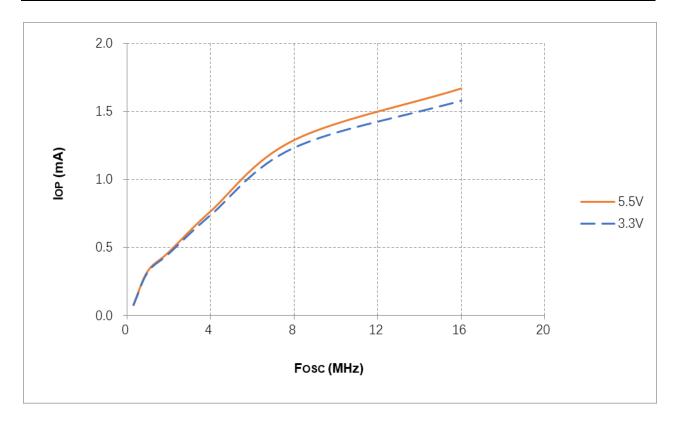

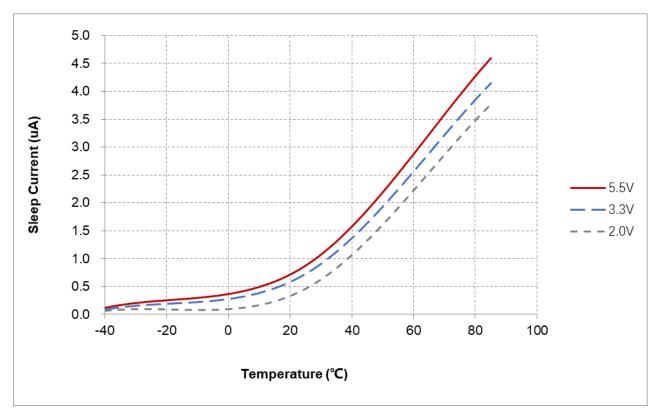

|     | 18.5   | Operatio    | on Current (I <sub>DD</sub> )             | 98  |

|     | 18.6   | Internal (  | Oscillators                               | 99  |

|     | 18.7   | ADC (10     | bit) and ADC VREF                         | 99  |

|     | 18.8   | Compara     | ator                                      | 101 |

|     | 18.9     | 4bit DAC (Reference voltage configuration) | 101 |

|-----|----------|--------------------------------------------|-----|

|     | 18.10    | Voltage Regulator Output Circuit           | 101 |

|     | 18.11    | Program and Data EEPROM                    | 102 |

|     | 18.12    | EMC characteristics                        | 102 |

| 19. | Chara    | cterization Graphs                         | 103 |

| 20. | PACK     | AGING INFORMATION                          | 106 |

| Co  | ntact In | formation                                  | 114 |

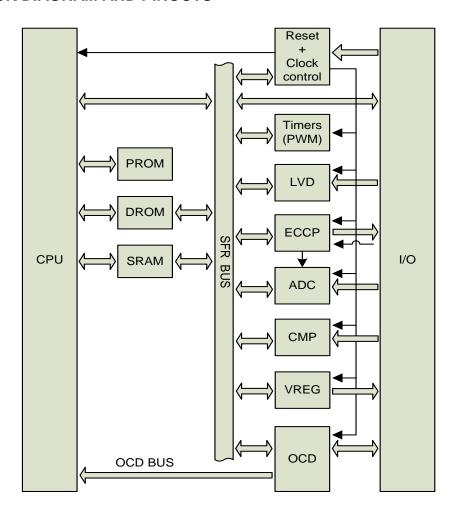

# 1. BLOCK DIAGRAM AND PINOUTS

Figure 1-1 System block diagram

The list of standard abbreviation is as follows:

| Abbreviation | Description                                         |

|--------------|-----------------------------------------------------|

| CPU          | Central Processing Unit                             |

| SFR          | Special Function Registers                          |

| SRAM         | Static Random Access Memory                         |

| DROM         | Data EEPROM                                         |

| PROM         | Program EEPROM                                      |

| Timers       | WDT, Timer0, Timer1, Timer2, Timer3, Timer4, Timer5 |

| PWM          | Pulse Width Modulator                               |

| ECCP         | Enhanced Capture Compare and PWM                    |

| ADC          | Analog to Digital Converter                         |

| CMP          | Comparator                                          |

| VREG         | Voltage Regulator                                   |

| LVD          | Low Voltage Detect                                  |

| OCD          | On Chip Debug                                       |

| I/O          | Input / Output                                      |

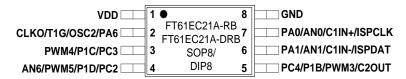

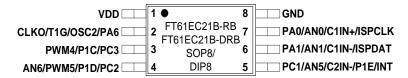

#### 1.1 Pinouts

**Figure 1-2** SOT23-6

**Figure 1-3** SOP8 / DIP8 (A)

**Figure 1-4** SOP8 / DIP8 (B)

Figure 1-5 MSOP10

Figure 1-6 SOP14 / DIP14

Figure 1-7 SOP16 / DIP16

# 1.2 Pin Description by Functions

| Function                   | Description                      | Pin<br>Name | GPIO equiv. | 6<br>pins | 8(A)<br>pins | 8(B)<br>pins | 10<br>pins | 14<br>pins | 16<br>pins |

|----------------------------|----------------------------------|-------------|-------------|-----------|--------------|--------------|------------|------------|------------|

| Power                      | VDD                              |             | 5           | 1         | 1            | 1            | 1          | 1          |            |

| rowei                      |                                  | GND         |             | 2         | 8            | 8            | 10         | 14         | 16         |

|                            |                                  | PC5         |             |           |              |              |            |            | 8          |

|                            |                                  | PC4         |             |           | 5            |              | 6          | 7          | 9          |

|                            |                                  | PC3         |             |           | 3            | 3            | 4          | 5          | 5          |

|                            |                                  | PC2         |             |           | 4            | 4            | 5          | 6          | 6          |

|                            |                                  | PC1         |             | 3         |              | 5            |            | 8          | 10         |

|                            | Dull Ho / Dull                   | PC0         |             |           |              |              |            | 9          | 11         |

| GPIO                       | Pull-Up / Pull-<br>Down, Digital | PA7         |             |           |              |              | 2          | 2          | 2          |

| GFIO                       | Input, Digital Output            | PA6         |             | 4         | 2            | 2            | 3          | 3          | 3          |

|                            | Catput                           | PA5         |             |           |              |              |            |            | 4          |

|                            |                                  | PA4         |             |           |              |              |            | 4          | 7          |

|                            |                                  | PA3         |             |           |              |              |            | 10         | 12         |

|                            |                                  | PA2         |             |           |              |              | 7          | 11         | 13         |

|                            |                                  | PA1         |             | 1         | 6            | 6            | 8          | 12         | 14         |

|                            |                                  | PA0         |             | 6         | 7            | 7            | 9          | 13         | 15         |

|                            | Output                           | CLKO        | PA6         | 4         | 2            | 2            | 3          | 3          | 3          |

|                            | Timer0 Clock                     | T0CKI       | PA2         |           |              |              | 7          | 11         | 13         |

| Clock                      | Timer1 Clock                     | T1CKI       | PA7         |           |              |              | 2          | 2          | 2          |

|                            | OSC +                            | OSC1        | PA7         |           |              |              | 2          | 2          | 2          |

|                            | OSC -                            | OSC2        | PA6         | 4         | 2            | 2            | 3          | 3          | 3          |

| Timer1 Gate input          |                                  | T1G         | PA6         | 4         | 2            | 2            | 3          | 3          | 3          |

| ICD Debugger               | ISP-Data                         | ISPDAT      | PA1         | 1         | 6            | 6            | 8          | 12         | 14         |

| ISP Debugger               | ISP-CLK                          | ISPCLK      | PA0         | 6         | 7            | 7            | 9          | 13         | 15         |

| Reset                      | Pull-up                          | /MCLRB      | PA5         |           |              |              |            |            | 4          |

| PC1-INT Edge               |                                  | INT         | PC1         | 3         |              | 5            |            | 8          | 10         |

|                            |                                  | PA7         |             |           |              |              | 2          | 2          | 2          |

|                            |                                  | PA6         |             | 4         | 2            | 2            | 3          | 3          | 3          |

|                            |                                  | PA5         |             |           |              |              |            |            | 4          |

| PORTA                      | Lancet                           | PA4         |             |           |              |              |            | 4          | 7          |

| Logic-Changes<br>Interrupt | Input                            | PA3         |             |           |              |              |            | 10         | 12         |

| ·                          |                                  | PA2         |             |           |              |              | 7          | 11         | 13         |

|                            |                                  | PA1         |             | 1         | 6            | 6            | 8          | 12         | 14         |

|                            |                                  | PA0         |             |           | 7            | 7            | 9          | 13         | 15         |

| Function            | Description         | Pin<br>Name       | GPIO equiv. | 6<br>pins | 8(A)<br>pins | 8(B)<br>pins | 10<br>pins | 14<br>pins | 16<br>pins |

|---------------------|---------------------|-------------------|-------------|-----------|--------------|--------------|------------|------------|------------|

| Voltage Regulator   | High voltage output | V <sub>REGP</sub> | PA4         |           |              |              |            | 4          | 7          |

| Voltage Negulator   | Low voltage output  | $V_{REGN}$        | PC5         |           |              |              |            |            | 8          |

|                     |                     | AN6               | PC2         |           | 4            | 4            | 5          | 6          | 6          |

|                     |                     | AN5               | PC1         | 3         |              | 5            |            | 8          | 10         |

|                     |                     | AN4               | PC0         |           |              |              |            | 9          | 11         |

| ADC                 | Input               | AN3               | PA3         |           |              |              |            | 10         | 12         |

| ADO                 |                     | AN2               | PA2         |           |              |              | 7          | 11         | 13         |

|                     |                     | AN1               | PA1         | 1         | 6            | 6            | 8          | 12         | 14         |

|                     |                     | AN0               | PA0         | 6         | 7            | 7            | 9          | 13         | 15         |

|                     | V <sub>REF</sub> +  | VREF              | PC0         |           |              |              |            | 9          | 11         |

|                     | Positive Input      | C1IN+             | PA0         | 6         | 7            | 7            | 9          | 13         | 15         |

| Comparator1         | Inverting Input     | C1IN-             | PA1         | 1         | 6            | 6            | 8          | 12         | 14         |

|                     | Output              | C1OUT             | PA2         |           |              |              | 7          | 11         | 13         |

|                     | Positive Input      | C2IN+             | PC0         |           |              |              |            | 9          | 11         |

| Comparator2         | Inverting Input     | C2IN-             | PC1         | 3         |              | 5            |            | 8          | 10         |

|                     | Output              | C2OUT             | PC4         |           | 5            |              | 6          | 7          | 9          |

|                     | Capture/Compare     | CCP1              | PC5         |           |              |              |            |            | 8          |

|                     |                     | P1A               | PC5         |           |              |              |            |            | 8          |

| Enhanced            |                     | P1B               | PC4         |           | 5            |              | 6          | 7          | 9          |

| Capture/Compare/PWM | PWM                 | P1C               | PC3         |           | 3            | 3            | 4          | 5          | 5          |

| (ECCP)              | FVVIVI              | P1D               | PC2         |           | 4            | 4            | 5          | 6          | 6          |

|                     |                     | P1E               | PC1         | 3         |              | 5            |            | 8          | 10         |

|                     |                     | P1F               | PC0         |           |              |              |            | 9          | 11         |

| PWM3                |                     | PWM3              | PC4         |           | 5            |              | 6          | 7          | 9          |

| PWM4                |                     | PWM4              | PC3         |           | 3            | 3            | 4          | 5          | 5          |

| PWM5                |                     | PWM5              | PC2         |           | 4            | 4            | 5          | 6          | 6          |

Table 1-1

Pin description by functions

#### 2. I/O PORTS

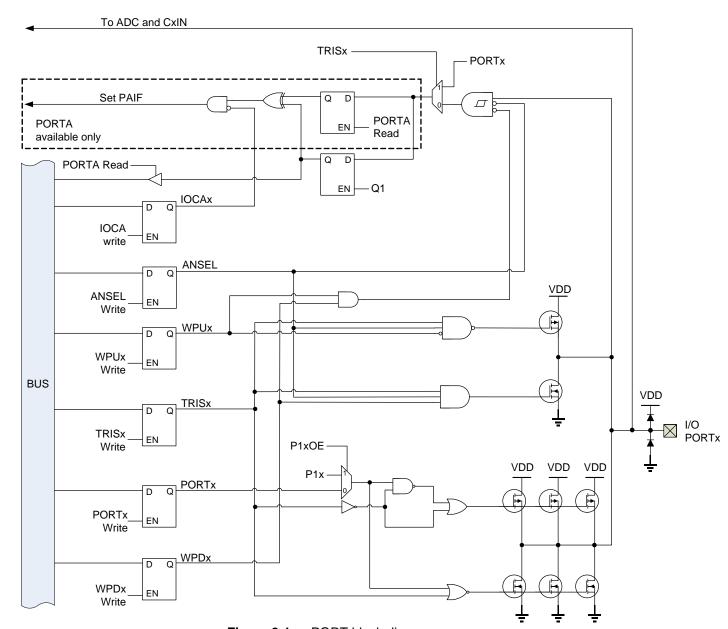

Up to 14 I/O pins are available depending on the types of package. I/O ports are divided into 2 groups: PORTA (8) and PORTC (6), **Table 2-1** lists the functions of all I/O pins.

Figure 2-1 PORT block diagram

All I/O pins have the following functions (Table 2-3, Table 2-4):

Digital Output

Weak Pull-Up

Digital Input

Weak Pull-Down (PA4, PC1, PC2, PC3)

In addition some I/O's have special functions assigned.

- a. Debugger pins (ISP-Data, ISP-CLK) are hardwired and require no set-up.

- b. Some special functions are configured at the IDE and loaded during BOOT (Table 2-2):

- External Clock (OSC1, OSC2)

- System-Reset (/MCLRB)

- Internal Clock OUT

- c. All other functions are Instruction Level assigned to the various I/O's. They are divided into 3 categories:

- a. Digital Output

- PWM3/4/5

- Enhanced PWM

- b. Digital Input

- Timer0 Clock Input

- Timer1 Clock Input

- Timer1 Clock Input

- c. Analog Input

- LVD / BOR

- ADC

- d. Analog Output

- Voltage Regulator output (V<sub>REG</sub>)

- ECCP output

- Comparator output CxOUT

- ECCP capture input

- External Edge Interrupt (INT)

- GPIO Interrupt-on-Change

- V<sub>REF</sub>

- Comparator input CxIN+ / CxIN-

| Name  | ISP<br>Debugger | CLK             | ADC                   | Voltage<br>Regulat<br>or | Comparat<br>or | Interrupt    | ECCP / PWM | Digitial I/O<br>Pull-Up/Down<br>Open Drain | Source<br>Current<br>(mA) | Sink<br>Current<br>(mA) |

|-------|-----------------|-----------------|-----------------------|--------------------------|----------------|--------------|------------|--------------------------------------------|---------------------------|-------------------------|

| PA0   | CLK             |                 | AN0                   |                          | C1IN+          | V            |            | √/                                         | 22                        | 19                      |

| PA1   | DATA            |                 | AN1                   |                          | C1IN-          | V            |            | √/                                         | 22                        | 19                      |

| PA2   |                 | T0CKI           | AN2                   |                          | C10UT          | $\sqrt{}$    |            | √/                                         | 22                        | 19                      |

| PA3   |                 |                 | AN3                   |                          |                | $\sqrt{}$    |            | √/                                         | 22                        | 19                      |

| PA4   |                 |                 |                       | $V_{REGP}$               |                | $\sqrt{}$    |            | <b>111</b>                                 | 22                        | 19                      |

| PA5   |                 |                 |                       |                          |                | √+<br>/MCLRB |            | √/                                         | 22                        | 19                      |

| PA6   |                 | output<br>/OSC- |                       |                          |                | √            |            | √/                                         | 22                        | 19                      |

| PA7   |                 | T1CKI<br>/OSC+  |                       |                          |                | <b>V</b>     |            | √/                                         | 22                        | 19                      |

| PC0   |                 |                 | AN4                   |                          | C2IN+          |              | P1F        | √/                                         | 22                        | 19                      |

| PC1   |                 |                 | AN5                   |                          | C2IN-          | INT          | P1E        | <b>111</b>                                 | 22                        | 19                      |

| PC2   |                 |                 | AN6                   |                          |                |              | PWM5 / P1D | <b>111</b>                                 | 22                        | 19                      |

| PC3   |                 |                 |                       |                          |                |              | PWM4 / P1C | <b>111</b>                                 | 22                        | 19                      |

| PC4   |                 |                 |                       |                          | C2OUT          |              | PWM3 / P1B | √/                                         | 22                        | 19                      |

| PC5   |                 |                 |                       | $V_{REGN}$               |                |              | CCP1 / P1A | √/                                         | 22                        | 19                      |

| Notes |                 | T1G=PA6         | V <sub>REF</sub> =PC0 |                          |                |              |            |                                            | V <sub>DD</sub> =5, \     | / <sub>DS</sub> =0.5    |

Table 2-1 I/O PORT Functions

# 2.1 Summary of I/O PORT Related Registers

| Name   | Function                                                                                                                                                                                                                                                                                            | Default  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RDCTRL | READ register when TRISx = 0 (Output enabled)  Input latch  Output latch                                                                                                                                                                                                                            | Output   |

| MCLRE  | Reset by External I/O                                                                                                                                                                                                                                                                               | disable  |

| FOSC   | <ul> <li>LP external oscillator across PA7 (+) and PA6 (-)</li> <li>XT external oscillator across PA7 (+) and PA6 (-)</li> <li>EC external oscillator at PA7 (+), PA6 as I/O</li> <li>INTOSC mode: PA6 output "Instruction Clock", PA7 as I/O</li> <li>INTOSCIO mode: PA7 and PA6 as I/O</li> </ul> | INTOSCIO |

Table 2-2 BOOT Level I/O related configurations

| Name   | Address | bit 7    | bit 6                                | bit 5    | bit 4                       | bit 3 | bit 2 | bit 1 | bit 0 | Reset Value |  |  |  |

|--------|---------|----------|--------------------------------------|----------|-----------------------------|-------|-------|-------|-------|-------------|--|--|--|

| ANSEL  | 0x91    | ANSEL [7 | ANSEL [7:0]                          |          |                             |       |       |       |       |             |  |  |  |

| TRISA  | 0x85    | TRISA[7: | 0], PORTA Di                         | irection |                             |       |       |       |       | 1111 1111   |  |  |  |

| TRISC  | 0x87    | -        | -                                    | PORTC    | Direction                   |       |       |       |       | 11 1111     |  |  |  |

| PORTA  | 0x05    | PORTA C  | Output Registe                       | er       |                             |       |       |       |       | XXXX XXXX   |  |  |  |

| PORTC  | 0x07    | -        | -                                    | PORTC    | Output Regi                 | ster  |       |       |       | xx xxxx     |  |  |  |

| WPUA   | 0x95    | PORTA V  | Veak Pull-Up                         |          |                             |       |       |       |       | 1111 1111   |  |  |  |

| WPUC   | 0x88    | -        | -                                    | PORTC    | Weak Pull-L                 | Jp    |       |       |       | 00 0000     |  |  |  |

| WPD    | 0x89    | -        | -                                    | -        | - WPDA4 WPDC1 WPDC2 WPDC3 - |       |       |       |       |             |  |  |  |

| IOCA   | 0x96    | IOCA[7:0 | IOCA[7:0]: PORTA Interrupt-on-Change |          |                             |       |       |       |       |             |  |  |  |

| OPTION | 0x81    | /PAPU    | INTEDG                               | T0CS     | T0SE                        | PSA   | PS2   | PS1   | PS0   | 1111 1111   |  |  |  |

Table 2-3

Addresses and Reset Values of I/O related registers

| Name  |                                                                                          | Status                                                         | Register   | Addr. | Reset        |

|-------|------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|-------|--------------|

| TRISA | PORTA                                                                                    | PORT Digital Output (Direction)                                | TRISA[7:0] | 0x85  | RW-1111 1111 |

| TRISC | PORTC                                                                                    | 1 = <u>Disables</u><br>0 = Enables (Disables Pull-<br>Up/Down) | TRISC[5:0] | 0x87  | RW-11 1111   |

| ANSEL | 1 = Disables Pull-Up / Pull-Down, Digital Input<br>(8 ADC ports only)<br>0 = (no action) |                                                                | ANSEL[7:0] | 0x91  | RW-1111 1111 |

| /PAPU | 1 = <u>Disables all PORTA Pull-Up</u><br>0 = WPUA settings apply                         |                                                                | OPTION[7]  | 0x81  | RW-1         |

| WPUA  | PORTA                                                                                    | Weak Pull-Up                                                   | WPUA[7:0]  | 0x95  | RW-1111 1111 |

| WPUC  | PORTC                                                                                    | 1 = Enables (PORTA defaults)<br>0 = Disables (PORTC defaults)  | WPUC[5:0]  | 0x88  | RW-00 0000   |

| WPDA4 | PORTA                                                                                    | Weak Pull-Down                                                 | WPD[4]     |       | RW-0         |

| WPDC  | PORTC                                                                                    | 1 = Enables<br>0 = <u>Disables</u>                             | WPD[3:1]   | 0x89  | RW-000       |

| PORTA | PORTA                                                                                    | Data Out Bagistar                                              | PORTA[7:0] | 0x05  | RW-xxxx xxxx |

| PORTC | PORTC                                                                                    | Data Out Register                                              | PORTC[5:0] | 0x07  | RW-xx xxxx   |

Table 2-4

Instruction Level I/O related registers

# 2.2 Configuring the I/O

For each PORT, configures the following four modules according to their functions (Table 2-5)

- Weak Pull-Up

- Weak Pull-Down (PA4, PC1, PC2, PC3)

- Digital Input

- Digital Output

| Functions            | Digital         | Pull-Up /  | Digital | Settings                          |

|----------------------|-----------------|------------|---------|-----------------------------------|

|                      | Input           | Pull-Down  | Output  | -                                 |

| ISP-DATA             | On              | Off        | On      | (hardwired, instructions ignored) |

| ISP-CLK              | On              | Off        | Off     | (hardwired, instructions ignored) |

| /MCLRB               | On              | Pull-Up    | Off     | (BOOT set, instructions ignored)  |

| CLOCK OUT            | (don't<br>care) | Off        | On      | (BOOT set, instructions ignored)  |

| OSC+ (EC)            | On              | (optional) | Off     | (BOOT set, instructions ignored)  |

| OSC+ / OSC- (LP, XT) | Off             | Off        | Off     | (BOOT set, instructions ignored)  |

| ADC                  | Off             | Off        | Off     | TRISx = 1; ANSELx = 1             |

| $V_{REF}$            | Off             | Off        | Off     | TRISx = 1; ANSELx = 1             |

| Comparator input     | Off             | Off        | Off     | TRISx = 1; ANSELx = 1             |

| Comparator output    | On              | Off        | On      | TRISx = 0                         |

| Timer0 Clock         | On              | (optional) | Off     | TRISx = 1                         |

| Timer1 Clock         | On              | (optional) | Off     | TRISx = 1                         |

| Timer1 Gate          | On              | (optional) | Off     | TRISx = 1                         |

| Timer3/4/5 Clock     | On              | (optional) | Off     | TRISx = 1                         |

| Interrupt-on-Change  | On              | (optional) | Off     | TRISx = 1                         |

| PC1-INT              | On              | (optional) | Off     | TRISx = 1                         |

| Digital input        | On              | (optional) | Off     | TRISx = 1                         |

| PWM                  | On              | Off        | On      | TRISx = 0                         |

| ECCP capture         | On              | (optional) | Off     | TRISx = 1                         |

| ECCP compare/PWM     | On              | Off        | On      | TRISx = 0                         |

| Voltage regulator    | (don't<br>care) | Off        | Off     | VREG_OE = 1                       |

| Digital Output       | On              | Off        | On      | TRISx = 0                         |

Table 2-5 Instruction Level I/O Configuration Flags and Registers

#### Notes:

- 1. TRISx = 0: "Digital Output" enabled, "Pull-Up / Pull-Down" disabled (WPDx, WPUx ignored).

- 2. TRISx = 1: "Digital Output" disabled.

- 3. ANSELx = 1: "Pull-Up", "Pull-Down", "Digital Input" disabled (WPDx and WPUx ignored).

- 4. Only way to turn off "Digital Input" by instructions is "ANSELx = 1".

- 5. "/PAPU = 1" disables "Weak Pull-Up" for all PAx. There are no equivalent bits for PCx.

- 6. /MCLR enabled: PA5's Weak Pull-Up enabled (WPUA[5] ignored); PORTA[5] read "0".

- 7. Writing the PORTx Data Out registers will output the logic level to the corresponding I/O. Write operations are 'Read-Modify-Write' operations, meaning PORTx latch (output or input) are read first, then modified and written back, as up to 8 I/O share the same register.

- 8. Digital Output and Digital Input can be inclusive. Some applications need both enabled simultaneously.

- 9. The IDE can globally choose which PORT latch (output or input) to READ when TRISx = 0.

- 10. In Full-Reset or System-Reset PORTx will not reset, but TRISx will reset to "1", disabling output.

- 11. Weak Pull-Up enabled, Weak Pull-Down disabled when they are opened simultaneously.

See Section 9 "Interrupts" for setting up PC1-INT and PORTA Interrupt-on-Change.

## 3. POWER-ON-RESET (POR)

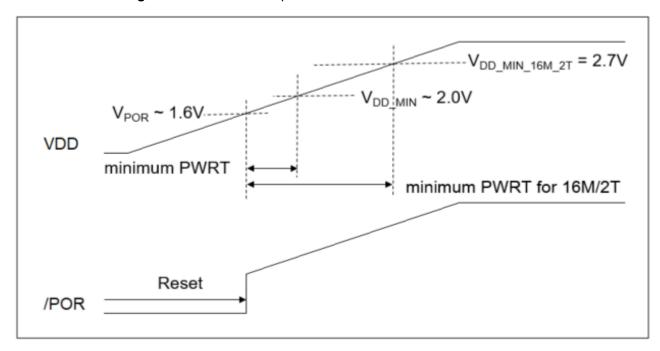

During Power-On,  $V_{DD}$  increases from below the Power-On-Reset Voltage ( $V_{POR}$ ) to above it.  $V_{DD}$  may not have completely discharged to 0V when the CPU is Power-On again.

- 1. The CPU is in a Full-Reset state when  $V_{DD}$  is below  $V_{POR}$ .

- a. All Calibrated Data registers are not reset. Special Function Registers (SFR) are in Reset, except TMR0, PORTx, Z, HC, C, FSR, INDF, ADRESL, ADRESH, TMRxL, TMRxH, CCPR1L, CCPR1H and SRAM (see Section 17 Special Function Registers). Registers not reset, such as SRAM, will hold their values until V<sub>DD</sub> drops below 0.6V (typical). Data of those resisters with V<sub>DD</sub> below 0.6V are undetermined.

- b. Program Counter = 0x00, Instruction Register = "NOP", Stack Pointer = "TOS" (Top of Stack).

- 2. BOOT commences when V<sub>DD</sub> raises above V<sub>POR</sub>.

- 3. Instruction execution begins with Program Counter = 0x00 after BOOT completion.

$V_{POR}$  is ~1.6V at 25°C (typical), increasing to ~1.9V at -40°C. For  $V_{DD} \ge V_{POR}$ , the CPU can function at a reduced speed of 8 MHz / 2T. POR alone can safeguard against a low  $V_{DD}$  failure, giving a self-regulated wider  $V_{DD}$  operating range with temperature. This is important for battery-powered system as the CPU can function down even to ~1.6V at typical battery operating environments, greatly extending useful battery life.

#### Notes:

- 1. V<sub>POR</sub> is not configurable.

- The POR circuit is always on and will perform a Power-On-Reset any time V<sub>DD</sub> voltage is below V<sub>POR</sub>, not just during Power-On.

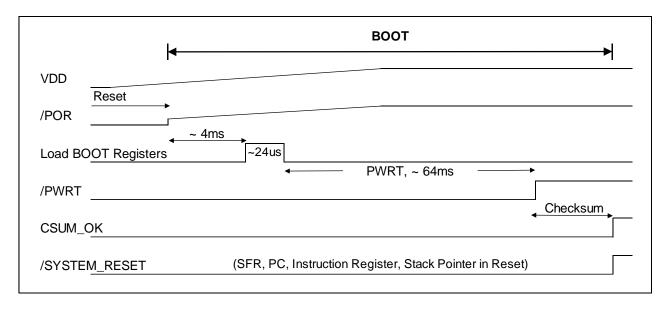

#### 3.1 BOOT Sequence

| Name    | Functions                              | default  |

|---------|----------------------------------------|----------|

| PWRTEB  | Additional ~64ms delay after BOOT load | disabled |

| CSUMENB | Array Checksum test                    | disabled |

**Table 3-1** BOOT configurations

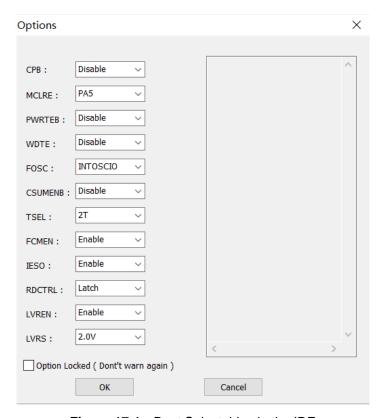

There are 2 BOOT configurations. Their values are set at the IDE, not by instructions. during BOOT:

- 1. CPU Idles for ~4ms.

- 2. The BOOT Level registers are loaded from the non-volatile memory. It takes ~24us. These registers are pre-set at the IDE and not affected by instructions.

- 3. If Power-On-Timer (PWRT) is enabled, the CPU will idle for ~64ms.

- 4. If the Checksum (CSUM) is enable, it will do a Checksum of the whole program array.

- a. If Checksum fail, it will BOOT again, starting with the ~4ms idle time.

- b. If Checksum pass, instructions execution will begin as long as there are no other Reset conditions.

Figure 3-1 Power-On Sequence with PWRT and Checksum enabled

Figure 3-2 Minimum required PWRT during Power-On

$V_{DD}$  must be higher than 2.5V by the end of BOOT if the CPU is to run at 16MHz / 2T. The total BOOT time can increase from ~4ms to ~68ms by enabling the PWRT, giving more time for the power system to stabilize.

Enables LVR with  $V_{BOR} \ge 2.5 V$  for operation at 16MHz / 2T. LVR can be set to instruction controlled to monitor  $V_{DD}$  sporadically, instead of always on (see "LVREN", "SLVREN") to reduce power consumption.

#### Notes:

- 1.  $V_{DD}$  should not rise too slowly.  $C_{VDD} \ge 22 \mu F$  is discouraged.

- 2.  $V_{DD}$  capacitor of 1 to 10 $\mu$ F is preferred.  $C_{VDD}$  < 1 $\mu$ F capacitor may be too small for EFT considerations.

- 3. If a delay in startup is acceptable, enables PWRT and CSUM to improve CPU stability.

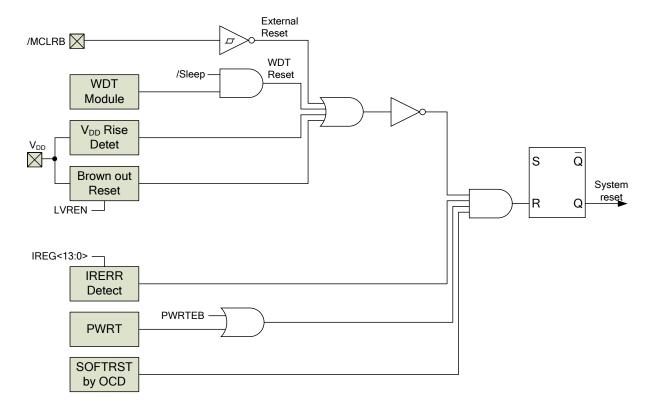

#### 4. SYSTEM-RESET

System-Reset differs from POR in that it is not a Full-Reset. Depending on the trigger type and configurations, CPU may or may not BOOT. BOOT will wait ~4ms, reload the BOOT registers, and further delay system start by ~64ms if PWRT is enabled. In a System-Reset

- Registers reset in POR are reset, except BOOT registers.

- Program Counter = 0x00, Instruction Register = "NOP", Stack Pointer = "TOS" (Top of Stack).

The following 4 events besides debugger OCD can be configured to trigger a System-Reset:

- 1. Brown-Out (LVR / BOR) always BOOT.

- 2. Illegal Instructions BOOT if "IRBTE" is set.

- 3. Watch-Dog Timer (WDT) BOOT if CPU not in SLEEP.

- 4. External I/O (/MCLRB) BOOT if "MRBTE" is set.

Note: If a longer system restart time is acceptable, enable BOOT will improve system stability.

Figure 4-1 Reset circuit block diagram

#### 4.1 Summary of SYSTEM-RESET Related Registers

Most settings for System-Reset are configured at the IDE, and cannot be changed by instructions.

| Name  | Functions                                                                         | default        |

|-------|-----------------------------------------------------------------------------------|----------------|

| LVRS  | 7 V <sub>BOR</sub> Voltage levels (V):<br>2.0 / 2.2 / 2.5 / 2.8 / 3.1 / 3.6 / 4.1 | 2.0            |

| LVREN | LVR  Enable  Disable  Enable except in SLEEP  Instruction controlled (SLVREN)     | disable        |

| WDTE  | WDT     Enable (overrides instructions disable)     Instruction controls (SWDTEN) | SWDTEN control |

| MCLRE | Reset by External I/O                                                             | disable        |

Table 4-1 BOOT Level RESET related configurations

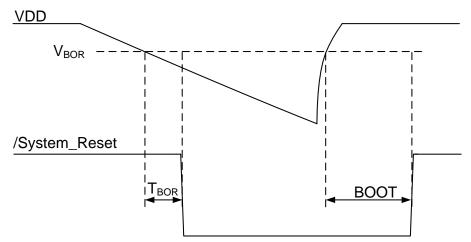

#### 4.2 Brown-Out Reset (LVR / BOR)

Brown-Out occurs when  $V_{DD}$  falls below a pre-configured Brown-Out Voltage ( $V_{BOR}$ ) for a time longer than  $T_{BOR}$ .  $T_{BOR}$  takes 3 to 4 LIRC clock cycles (~94 – 125µs, LIRC will turn on automatically if not already). CPU System-Reset as long as  $V_{DD} \le V_{BOR}$ . Once  $V_{DD} > V_{BOR}$  CPU will BOOT.

While  $V_{POR}$  is fixed,  $V_{BOR}$  can be set to 2.0, 2.2, 2.5, 2.8, 3.1, 3.6, 4.1V (see "LVRS" in Table 4-1).

Figure 4-2 LVR BOOT Timing Diagram

LVR function can have four different settings configured by BOOT (see "LVREN" in Table 4-1).

- 1. LVR enabled.

- 2. LVR disabled.

- 3. LVR enabled, except in SLEEP.

Rev1.03 - 19 - 2025-03-28

4. Let instructions enable or disable LVR (SLVREN, see Table 4-2).

Note: LVR can be instructions disabled in SLEEP to reduce power consumption. The CPU should wake up and enable LVR periodically to monitor  $V_{DD}$  if system  $V_{DD}$  is unstable.

| Name   | Status                                          | Register   | Addr. | Reset |

|--------|-------------------------------------------------|------------|-------|-------|

|        | Applies only when LVREN cedes control to SLVREN |            |       |       |

| SLVREN | 1 = Enables LVR                                 | MSCKCON[4] | 0x1B  | RW-0  |

|        | 0 = <u>Disables LVR</u>                         |            |       |       |

Table 4-2 Instruction Level LVR registers

Note: SLVREN can be cleared by any system reset except BOR

#### 4.3 Illegal Instruction Reset

There are many reasons a CPU fetches an instruction incorrectly, with interference and  $V_{DD}$  instability the most common. When such an event occurs System-Reset and/or BOOT.

#### 4.4 Watch Dog Timer, WDT Reset

WDT overflows during SLEEP will result in a Wake-Up.

WDT overflows not during SLEEP will trigger a System-Reset. The IDE preset if a BOOT follows (see "WDTE" in **Table 4-1**). This can reset a hanged CPU. Clear WDT from time to time in the program to avoid false reset.

For details on WDT operation and setting see Section 7.1 Watch Dog Timer (WDT).

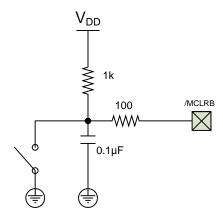

#### 4.5 External System-Reset /MCLRB

The CPU can be reset by a low voltage applied to the /MCLRB (PA5) pin if so configured by BOOT. The /MCLRB pin is usually soft pullup to  $V_{DD}$  with a resistor instead of directly, as shown in **Figure 4-3**. The external RC network also provides glitches filtering and over-current protection.

Figure 4-3 /MCLRB reset circuit

# 4.6 Detecting the Type of Reset Last

Four status flags /POR, /BOR, Time Out (/TF), Power Down (/PF) together can trace the type of last System-Reset, except between "/MCLR System-Reset during normal operation" and "Illegal Instruction Reset". Use instructions to set the flags to "1". In a Reset, the corresponding flag(s) latches to "0".

|                                          | /POR    | /BOR      | /TF           | /PF          |

|------------------------------------------|---------|-----------|---------------|--------------|

| Reset Source                             | PCON[1] | PCON[0]   | STATUS[4]     | STATUS[3]    |

|                                          | 0x      | (8E       | 0x03, 0x83, 0 | 0x103, 0x183 |

| POR                                      | 0       | (unknown) | 1             | 1            |

| LVR                                      | _       | 0         | 1             | 1            |

| WDT overflows while not in SLEEP (Reset) | _       | _         | 0             | _            |

| WDT overflows while in SLEEP (Resume)    | _       | _         | 0             | 0            |

| /MCLR Reset during SLEEP                 | _       | _         | 1             | 0            |

| /MCLR Reset during normal operation      | _       | -         | -             | _            |

| Illegal Instruction                      | _       | _         | _             | _            |

| On-Chip Debugger (OCD)                   | _       | _         | _             | _            |

Table 4-3 Reset Related Status Flags ("-" no change)

# 5. LOW VOLTAGE DETECT / COMPARATOR (LVD)

LVD works similarly to a LVR except for the followings:

- None of the control and setting parameters are set by BOOT. They are set by instructions.

- It will write LVDW instead of /BOR.

- The input to the LVD module can be configured to V<sub>DD</sub>. The latter allows the LVD to function as a single input comparator to one of the six LVDL levels.

- Debouncing Time ( $T_{LVD}$ ) is much shorter than  $T_{BOR}$  at 3 4 HIRC cycles (~94 125 $\mu$ s, LIRC turns on automatically if not already so).

#### 5.1 Summary of LVD Related Registers

| Name  |                      | Status                              | Register  | Addr. | Reset  |

|-------|----------------------|-------------------------------------|-----------|-------|--------|

| LVDEN | <u>LVD</u>           | 1 = Enables<br>0 = <u>Disables</u>  | PCON[3]   |       | RW-0   |

|       |                      | 000 = Reserved<br>001 = Reserved    |           | 0x8E  |        |

| LVDL  | V <sub>lvd-ref</sub> | 010 = 2.0<br>011 = 2.4<br>100 = 2.8 | PCON[6:4] |       | RW-000 |

|       |                      | 101 = 3.0<br>110 = 3.6              |           |       |        |

|       |                      | 111 = 4.0                           |           |       |        |

| LVDW  | LVD<br>triggered?    | 1 = Yes (no latch)<br>0 = No        | PCON[2]   |       | RO-x   |

Table 5-1 Instruction Level LVD Settings and Flags

#### 6. OSCILLATORS and SYSCLK

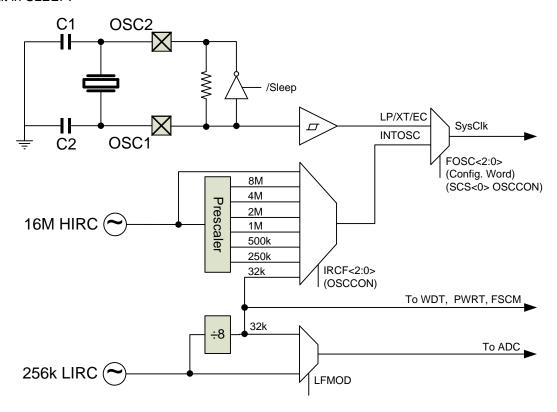

Instruction chooses whether SysClk is the internal oscillator HIRC, internal oscillator LIRC, or one of the three external oscillators (EC, LP, XT, see "SCS" in **Table 6-2**). If external oscillator is chosen, BOOT level "FOSC" (**Table 6-1**) will determine which one of the three external oscillators is used. Instructions also select the frequency step down divider for internal oscillator (see IRCF in **Table 6-2**). SysClk is used to derive the Instruction Clock:

Instruction Clock = SysClk / N; N = 2 for 2T, 4 for 4T.

The pin assignments for external clock inputs and Instruction Clock output are set by BOOT (see FOSC).

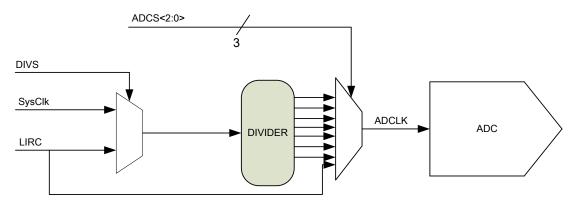

Timers and ADC have their own oscillators. More than one oscillator can be active simultaneously.

Oscillators will turn on automatically when the Timers using them are enabled. They will remain active as long as the corresponding Timers are active. The oscillators can be configured to shutdown or be active in SLEEP. By keeping the corresponding oscillator active in SLEEP, ADC, Timer functions and PWM can also be active in SLEEP.

As instructions are halted in SLEEP, so will Instruction Clock. Any peripherals using Instruction Clock will also halt in SLEEP.

Figure 6-1 Clock source block diagram for SysClk

#### 6.1 **Summary of Oscillator Modules Related Registers**

| Name  | Functions                                                                                                                                                                                                                                                                                                         | default  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| FOSC  | <ul> <li>LP external oscillator across PA7 (+) and PA6 (-)</li> <li>XT external oscillator across PA7 (+) and PA6 (-)</li> <li>EC external oscillator at PA7 (+), PA6 as I/O pin</li> <li>INTOSC mode: PA6 output "Instruction Clock", PA7 as I/O pins</li> <li>INTOSCIO mode: PA7 and PA6 as I/O pins</li> </ul> | INTOSCIO |

| IESO  | Two-speed Startup for XT and LP                                                                                                                                                                                                                                                                                   | Enable   |

| FCMEN | Fail-Safe Clock Monitor                                                                                                                                                                                                                                                                                           | Enable   |

| TSEL  | # of SysClk per Instruction (2T or 4T)  • 2 (Instruction Clock = SysClk/2)  • 4 (Instruction Clock = SysClk/4)                                                                                                                                                                                                    | 2        |

Table 6-1 BOOT Level FOSC and 2-speed Start-Up configurations

|               |       |                      |           | configu     | ration    |        |  |

|---------------|-------|----------------------|-----------|-------------|-----------|--------|--|

|               |       |                      | SCS       | IRCF        | LFMOD     | OST    |  |

| SysClk Source |       |                      | OSCCON[0] | OSCCON[6:4] | OSCCON[7] |        |  |

|               |       |                      |           | 0x8F        |           |        |  |

|               |       |                      | RW-0      | RW-101      | RW-0      |        |  |

|               | EC    |                      | 0         | -           | -         | -      |  |

| External      | XT    |                      | 0         | -           | -         | 1,024  |  |

|               | LP    |                      | 0         | -           | -         | 32,768 |  |

|               | HIRC  | 16 MHz               | 1         | 111         | -         | -      |  |

|               |       | 8 MHz                | 1         | 110         | -         | -      |  |

|               |       | 4 MHz                | 1         | <u>101</u>  | -         | -      |  |

|               |       | 2 MHz                | 1         | 100         | -         | -      |  |

| Internal      |       | 1 MHz                | 1         | 011         | -         | -      |  |

|               |       | 500 kHz              | 1         | 010         | -         | -      |  |

|               |       | 250 kHz              | 1         | 001         | -         | -      |  |

|               | LIRC  | 256 kHz <sup>1</sup> | 1         | 000         | 1         | -      |  |

|               | LIICO | 32 kHz <sup>2</sup>  | 1         | 000         | 0         | -      |  |

Table 6-2 Instruction Level SysClk source setup

$<sup>^{\</sup>rm 1}\,$  256 kHz LIRCs used only for ADC (see ADCS and LFMOD in Table 12-2 ).

<sup>&</sup>lt;sup>2</sup> Sysclk source (IRCF=000), LIRC and HIRC Cross Calibration, PWRT and FSCM all use the 32kHz LIRC, regardless of the LFMOD value.

remont Micro Devices FT61EC2x

| Name   | Status                                                                                                                                       | Register     | Addr.             | Reset  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|--------|

| OSTS   | Oscillator Start-Up Time-out (latched)?  1 = Running from the external clock (start-up successful)  0 = Running from the internal oscillator | OSCCON[3]    |                   | RO-x   |

| HTS    | HIRC ready (latched)?  1 = Yes  0 = No                                                                                                       | OSCCON[2]    | 0x8F              | RO-0   |

| LTS    | <u>LIRC ready (latched)?</u><br>1 = Yes<br>0 = <u>No</u>                                                                                     | OSCCON[1]    |                   | RO-0   |

| CKMAVG | 4x averaging for LIRC and HIRC Cross  Calibration  1 = Enables  0 = Disables                                                                 | MSCKCON[2]   | 0x1B              | RW-0   |

| CKCNTI | Initiate LIRC and HIRC Cross Calibration  1 = Start  0 = Finished (auto-cleared)                                                             | MSCKCON [1]  |                   | RW-0   |

| SOSCPR | LIRC Period Calibrated by # of HIRC clocks                                                                                                   | SOSCPR[11:0] | 0x1D[3:0]<br>0x1C | RW-FFF |

Table 6-3 Oscillators Control/Status

| Name    |                                         | Status                                                                                | Register  | Addr.        | Reset |

|---------|-----------------------------------------|---------------------------------------------------------------------------------------|-----------|--------------|-------|

| GIE     | Global Interrupt                        | 1 = Enables (PEIE, CKMEAIE, OSFIE applies) 0 = Global Disables (Wake-Up not affected) | INTCON[7] | 0x0B<br>0x8B | RW-0  |

| PEIE    | Master Peripheral<br>Interrupt          | 1 = Enables (CKMEAIE, OSFIE applies) 0 = <u>Disables</u> (no Wake-Up)                 | INTCON[6] | 0x10B        | RW-0  |

| CKMEAIE | LIRC Calibration<br>Completed Interrupt | 1 = Enables<br>0 = <u>Disabled</u><br>(no Wake-Up)                                    | PIE1[6]   | 0.400        | RW-0  |

| OSFIE   | External Oscillator<br>Failed Interrupt | 1 = Enables<br>0 = <u>Disabled</u><br>(no Wake-Up)                                    | PIE1[2]   | 0x8C         | RW-0  |

| CKMEAIF | LIRC Calibration completed?             | 1 = Yes (latched)<br>0 = <u>No</u>                                                    | PIR1[6]   | 0,400        | RW-0  |

| OSFIF   | External Oscillator Failed interrupt?   | 1 = Yes (latched)<br>0 = <u>No</u>                                                    | PIR1[2]   | 0x0C         | RW-0  |

Table 6-4 Oscillators Interrupt enable/Status

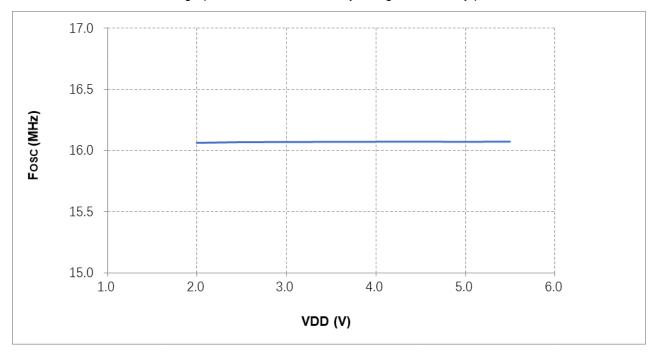

#### 6.2 Internal Clock Modes (HIRC and LIRC)

Internal high frequency clock (HIRC) is factory calibrated to 16 MHz, calibration range  $< \pm 1.0\%$  @2.5V/25°C. Typical variation of supply voltage is  $< \pm 1.0\%$  @2.5-5.5V/25°C. The temperature dependence is  $< \pm 3.0\%$  @ $^{-}40 - ^{+}85$ °C/2.5V.

HIRC is calibrated at the wafer level. Packaging may cause the HIRC frequency to drift. There is an option at the downloader to re-calibrate the HIRC.

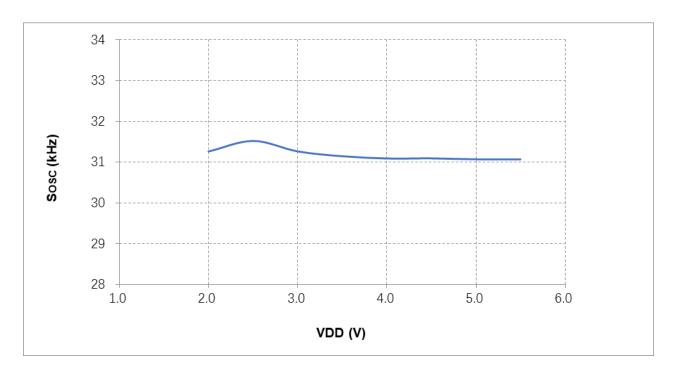

**Internal low frequency clock (LIRC)** is factory calibrated to 32 kHz, calibration range  $< \pm 5.0\%$  @2.5V/25°C. Typical variation of supply voltage is  $< \pm 4.0\%$  @2.5-5.5V/25°C. The temperature dependence is  $< \pm 2.0\%$  @ $^{-}40 - ^{+}85$ °C/2.5V.

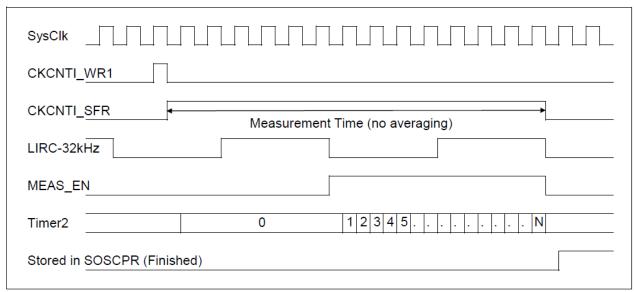

LIRC and HIRC can be used to cross calibrate each other – A build in hardware uses Timer2 to measure the number of Instruction Clocks (set SysClk to HIRC at 16MHz) in one LIRC period (32 kHz). Since LIRC has a lower temperature coefficient, the HIRC can be calibrated to the LIRC when the temperature fluctuates, thereby achieving the same ±2.0% temperature coefficient.

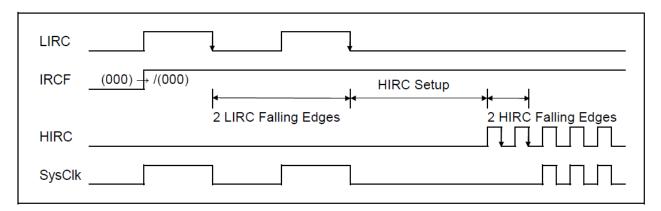

Figure 6-2 Single measurement timing diagram

To enable LIRC and HIRC Cross Calibration:

- 1. Set IRCF = 111, SCS = 1 ; select SysClk at 16MHz HIRC (other settings will have a lower accuracy).

- 2. Set CKMAVG = 1 ; 4 times averaging, choose 0 for no averaging.

- 3. Set TMR2ON = 1 ; enable Timer2.

- 4. Set CKCNTI = 1 ; start calibration, automatically Timer2 prescaler = 1, postscalar = 1, T2CKSRC = SysClk for 2T; SysClk/2 for 4T

- 5. At the end of the calibration "CKCNTI = 0", "CKMEAIF = 1" automatically.

- 6. Measured value is stored at SOSCPR:

- 7. LIRC is 32kHz and CPU is running at 16MHz / 2T, the ideal matching number is 500.

#### Notes:

- Do not write SOSCPRH/L during LIRC and HIRC Cross Calibration.

- Timer2 cannot be used by other peripherals during LIRC and HIRC Cross Calibration.

- LIRC and HIRC Cross Calibration is incompatible with Single Step Debugger mode.

#### 6.3 External Clock Modes (EC / LP / XT)

#### 6.3.1 EC mode

External digital signal connected to OSC1 is the clock source (OSC2 is available for I/O). There is no set up or transition time delay when EC is used for SysClk after a POR or a wake-up from sleep.

#### 6.3.2 LP and XT modes

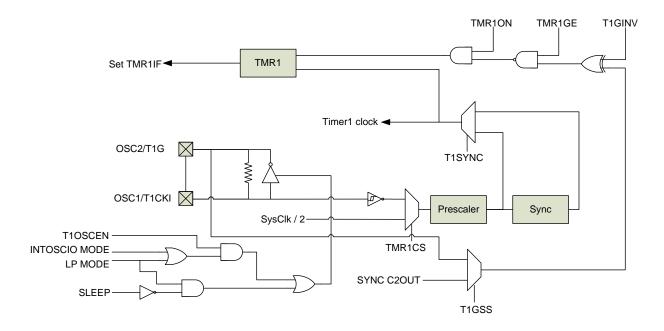

A quartz crystal resonator or ceramic resonator is connected between OSC1 and OSC2 in LP or XT modes.

**LP Oscillator** mode has the lowest gain setting and current consumption of the three modes (EC, LP and XT). This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

XT Oscillator mode selects the highest gain setting of the internal inverter-amplifier.

After a BOOT or a Wake-Up from Sleep, program execution is suspended during OST counting if the clock source is XT or LP mode. This allows the XT or LP clock to stabilize. OST counts 1,024 or 32,768 counts of OSC1 (+ve terminal of the crystal input) for XT and LP respectively. For a 32.768 kHz tuning-fork type crystals the OST time is at least 1 second.

Notes: WDT is held in cleared until OST finished counting. Do not write WDTCON / OPTION during OST counting, otherwise unexpected behavior will occur.

**Two-Speed Clock Start-up** (see "IESO" in **Table 6-1**) allows instructions execution while OST counts, using the internal oscillator INTOSC as SysClk. It removes the external oscillator start-up time from the time spent awake and can reduce the overall power consumption, especially in cases of frequent SLEEP mode usage. The CPU wakes up from Sleep, performs a few instructions using the INTOSC as SysClk and return to Sleep without having to wait for the primary oscillator to become stable.

Note: Two-Speed Start-up is disabled for EC mode, as the oscillator does not require stabilization time.

Two Speed Start-up sequence

- 1. After a BOOT or Wake-up from Sleep.

- 2. INTOSC is used as SysClk for Instructions execution until OST time out.

- SysClk is held low from the falling edge of INTOSC until the falling edge of the new clock (LP or XT mode).

- 4. SysClk switches to the external clock source.

The Oscillator Start-up Time-out Status (OSTS) indicates whether the SysClk is running from the external clock source or from the internal clock source. This is an indirect way to find out if the Oscillator Start-up Timer (OST) has timed out for the LP or XT mode when the Two-Speed Clock Start-up mode is on.

Executing a SLEEP instruction will abort the OST, and OSTS will remain "0".

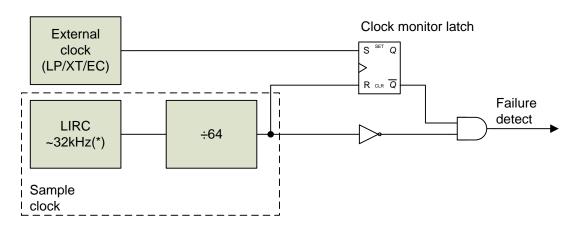

**Fail-Safe Clock Monitor** (FSCM, enabled by "FCMEN", see **Table 6-1**) allows the device to continue operating should the external oscillator fails. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is applicable to all external oscillator modes (EC, LP and XT). It is recommended that FSCM be enabled if an external oscillator is used.

An external oscillator is considered fail if it oscillates at ~1 kHz or below. A sample clock is generated by dividing the LIRC by 64. The external clock sets a latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is when an entire half-cycle of the sample clock elapses without the primary clock goes low.

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets OSFIF. Setting this flag will generate an interrupt if OSFIE is also set. The device hardware can then take steps to mitigate the problems that may arise from a failed clock. The SysClk will continue to be sourced from the internal clock source until the device hardware successfully restarts the external oscillator.

The internal clock source chosen by "FSCM" is determined by "IRCF". This allows the internal oscillator to be configured before a failure occurs.

Note: LFMOD does not affect the sample clock.

Figure 6-3 FSCM block diagram

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS. When SCS is toggled, OST is restarted. While OST is running, the device continues to operate from INTOSC. When OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be resolved before the OSFIF flag is cleared.

Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, will not update SCS. The program can monitor OSTS to determine the current SysClk source.

#### 6.4 HIRC, LIRC and EC inter-switching

**Figure 6-4** shows the timing during inter-switching. If either HIRC or LIRC is shutdown prior to switching (to save power) there is an extra oscillator setup delay time, HTS and LTS indicate the status of the corresponding oscillator respectively.

Figure 6-4 Switching from LIRC to HIRC (same principle applies switching among EC, LIRC, HIRC)

# 7. TIMERS and PWMx

There are 7 Timers including the Watch Dog Timer (WDT).

|                  | WDT               | Timer0                                               | Timer1                                                                                     | Timer2                           | Timer3/4/5                                                                                                                                          |

|------------------|-------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Prescaler (bit)  | -                 | 8 (WDT shared)                                       | 3 (1x, 2x, 4x, 8x)                                                                         | 4 (1x, 4x, 16x)                  | 7 (1x, 2x, 4x, 8x,<br>16x, 32x, 64x, 128x)                                                                                                          |

| Counter (bit)    | 16                | 8                                                    | 16                                                                                         | 8                                | 12                                                                                                                                                  |

| Postscaler (bit) | 7 (Timer0 shared) | -                                                    | -                                                                                          | 4 (1 - 16x)                      | -                                                                                                                                                   |

| Clock Sources    | • <u>LIRC</u>     | Instruction Clock     PA2/T0CKI (transition counter) | <ul> <li>Instruction Clock</li> <li>LP</li> <li>PA7/T1CKI (rising edge counter)</li> </ul> | 2x Instruction Clock     2x HIRC | <ul> <li>HIRC</li> <li>2x Instruction Clock</li> <li>PA2/T0CKI<br/>(transition counter)</li> <li>PA7/T1CKI<br/>(rising edge<br/>counter)</li> </ul> |

Table 7-1 Timers' Resources

Notes: If a Timer's clock is not the instruction Clock, set "TMRxON = 0" before changing TMRx.

Any Timer enabled will turn on its clock source automatically. Instruction Clock is disabled at SLEEP so it cannot be used for WDT. When LP or XT Oscillator is selected, FOSC must be configured correspondingly or to INTOSCIO mode, otherwise the oscillator is off and no counting will occur.

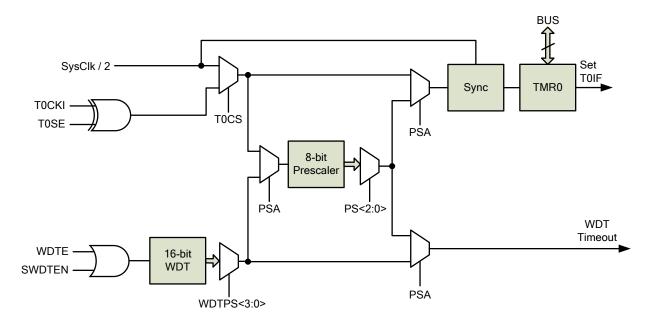

WDT postscaler and Timer0 prescaler shares the same hardware. The hardware is Instruction Level assigned to one, but not both. The Timer not assigned the scaler will have a scaler value of "1".

<u>In a POR or System-Reset, all Timers' counter, prescaler, postscalar are reset except Timer0 counter</u>. The followings will also reset a Timer's counter and scaler(s):

|            | WDT                                                                                                     | Timer0                                             | Timer1                                                                                                                               | Timer2                                                                                                                     | Timer3/4/5                          |

|------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Prescaler  | -                                                                                                       | <ul><li>TMR0 write</li><li>PSA switching</li></ul> | <ul><li>TMR1ON = 0</li><li>TMR1L/H write</li></ul>                                                                                   | <ul> <li>LIRC and<br/>HIRC Cross<br/>Calibration<br/>start</li> <li>T2CON,<br/>TMR2L/H write</li> <li>Any Reset</li> </ul> | TMRxL/H write                       |

| Counter    | <ul> <li>WDT, OST overflow</li> <li>Enters/Exits SLEEP</li> <li>CLRWDT</li> <li>WDTCON write</li> </ul> | Timer0 overflows                                   | <ul> <li>TMR1 = PR1         (matches,         special event         triggger)</li> <li>ECCP trigger         special event</li> </ul> | • TMR2 = PR2 (matches)                                                                                                     | TMRx = PRx (matches in BUZZER mode) |

| Postscaler | All Above except WDTCON write     PSA switching                                                         |                                                    | _                                                                                                                                    | T2CON, TMR2L/H write Any Reset                                                                                             | -                                   |

Table 7-2 Events reseting a Timer's Counter and Scaler(s)

#### 7.1 Watch Dog Timer, WDT

WDT is used to "Wake-Up from SLEEP" or "System-Reset if the CPU stalls". WDT counts the number of clock cyles to a pre-set number until overflow.

- In SLEEP mode, a WDT overflow will trigger a Wake-up. The CPU will resume operation from where it is before SLEEP. This is not an Interrupt nor System-Reset event.

- In non-SLEEP mode, a WDT overflow will trigger a System-Reset (see Section 4 System-Reset).

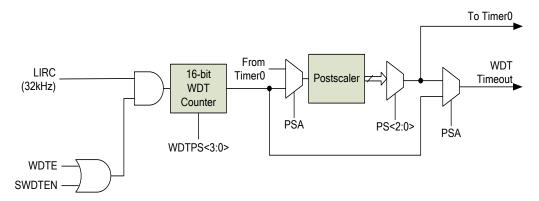

Figure 7-1 Block diagram of WDT

The WDT will overflow after a WatchDog-Time: WDT-Period x WDT-Postscaler / WDT Clock Frequency.

For a given Clock Source, WatchDog-Time step doubles successively due to the binary nature of the WDT Postscalar. Using LIRC as clock source, the maximum settable time before WDT overflows is

$$2^{16} \times 2^{7} / 32 \text{kHz} = ~262 \text{ seconds}.$$

# 7.1.1 Summary of WDT Related Registers

| Name   |                                                                                                                                                                                                                                                         |                               | Status     | Register  | Addr.       | Reset         |         |         |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------|-----------|-------------|---------------|---------|---------|

| WDTPS  | WDT Period       0000 = 32     0111 = 4,096       0001 = 64     1000 = 8,192       0010 = 128     1001 = 16,384       0011 = 256     1010 = 32,768       0100 = 512 (Default)     1011 = 65,536       0101 = 1,024     11xx = 65,536       0110 = 2,048 |                               |            |           | WDTCON[4:1] | 0x18          | RW-0100 |         |

| SWDTEN | 1 = WDT E<br>0 = <u>WDT D</u>                                                                                                                                                                                                                           | nables<br><u>Disables</u> (WD | TE = 0)    | WDTCON[0] |             | RW-0          |         |         |

| PSA    | 1 = <u>Scalar assigned as WDT Postscalar</u><br>0 = Scalar assigned as Timer0 Prescalar                                                                                                                                                                 |                               |            |           |             | OPTION[3]     |         | RW-1    |

|        | WDT Postscalar Timer0 Prescalar                                                                                                                                                                                                                         |                               |            |           |             |               |         |         |

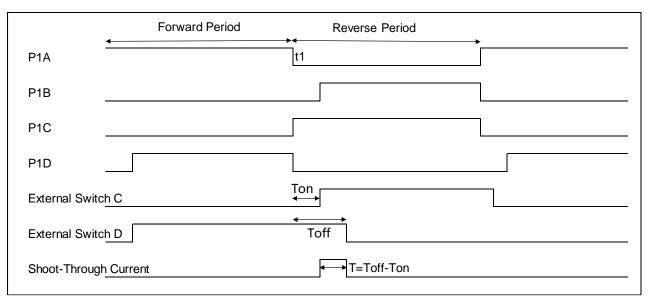

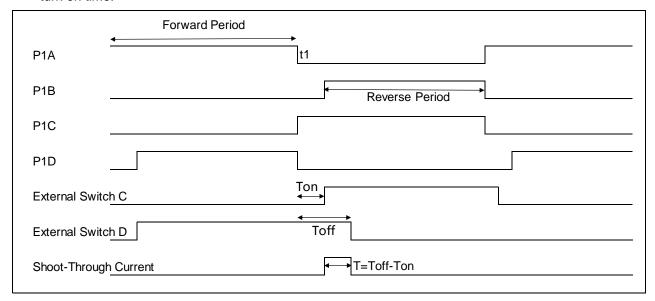

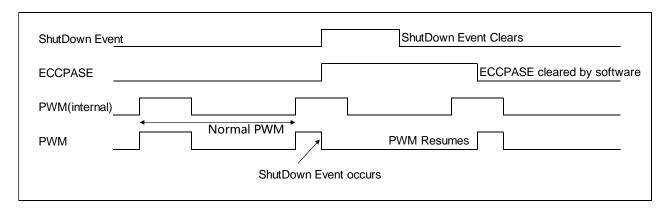

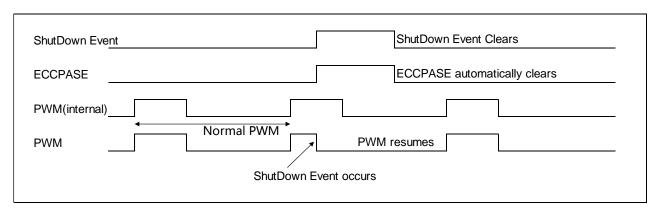

|        | 000                                                                                                                                                                                                                                                     |                               | 1          |           | 2           |               |         |         |