# SN74ACT2152A, SN74ACT2154A 2K×8 CACHE ADDRESS COMPARATORS

N PACKAGE

D3156, DECEMBER 1988-REVISED MARCH 1990

- Fast Address to Match Delay 20 or 25 ns Max

- Common I/O with Read Feature

- On-Chip Address/Data Comparator

- On-Chip Parity Generator and Checking

- Parity Error Output, Force Parity Error Input

- Easily Expandable

- Choice of Open-Drain or Totem-Pole MATCH Output

- EPIC™ (Enhanced Performance Implanted CMOS) 1-μm Process

- Fully TTL-Compatible

### description

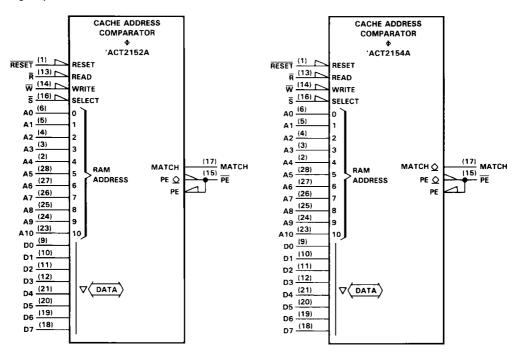

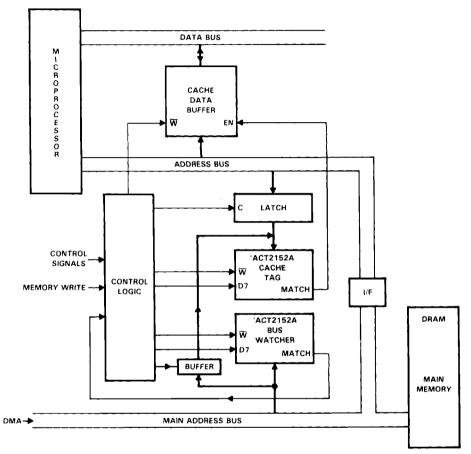

The 'ACT2152A and 'ACT2154A cache address comparators consist of a high-speed 2K × 9 static RAM array, parity generator, parity checker, and 9-bit high-speed comparator. They are fabricated using advanced silicon-gate CMOS technology for high speed and simple interface with bipolar TTL circuits. These cache address comparators are easily cascadable for wider tag addresses or deeper tag memories. Significant reductions in cache memory component count, board area, and power dissipation can be achieved with these devices. The 'ACT2152A has a totem-pole MATCH output while the 'ACT2154A has an open-drain MATCH output for easy AND-tying.

If  $\overline{S}$  is low and  $\overline{W}$  and  $\overline{R}$  are high, the cache address comparator compares the contents of the memory location addressed by AO-A10 with the data DO-D7 plus generated parity. An equality is indicated by a high level on the

FN PACKAGE (TOP VIEW)

MATCH output. A low-level output on  $\overline{PE}$  signifies a parity error in the internal RAM data.  $\overline{PE}$  is an N-channel open-drain output for easy OR-tying. During a write cycle ( $\overline{S}$  and  $\overline{W}$  low), data on D0-D7 plus generated odd parity are written in the 9-bit memory location addressed by A0-A10. Also during write, a parity error may be forced by holding  $\overline{PE}$  low.

EPIC is a trademark of Texas Instruments Incorporated.

These devices are covered by U.S. Patents 4,831,625; 4,858,182; 4,884,270; and additional patents pending

A read mode is provided with the 'ACT2152A and 'ACT2154A, which allows the contents of RAM to be read at the D0-D7 pins. The read mode is selected when  $\overline{R}$  and  $\overline{S}$  are low, and  $\overline{W}$  is high.

A reset input is provided for initialization. When  $\overline{\text{RESET}}$  is taken low, all 2K  $\times$  9 RAM locations are cleared to zero (with valid parity) and the MATCH output is forced high. If an input data word of zero is compared to any memory location that has not been written into since reset, MATCH will be high indicating that input data, plus generated parity, is equal to the reset memory location.  $\overline{\text{PE}}$  will be high after reset for every addressed memory location, indicating no parity error in the RAM data. By tying a single data input pin high, this bit will function as a valid bit and a match will not occur unless data has been written into the addressed memory location. When cascading in the width direction, only one bit must be tied high regardless of the address width.

These cache address comparators operate from a single +5-V supply and are offered in 28-pin plastic 600-mil ceramic side brazed, dual-in-line and PLCC packages.

The 'ACT2152A and 'ACT2154A are characterized for operation from 0°C to 70°C.

#### MATCH OUTPUT DESCRIPTION

$$\begin{split} \text{MATCH} &= \text{VOH if: } \underbrace{[\text{AO-A10}]}_{\text{RESET}} = \text{Vol}, \\ \text{or: } & \overline{\text{RESET}} = \text{Vol}, \\ \text{or: } & \overline{\text{S}} = \text{Vol}, \\ \text{or: } & \overline{\text{W}} = \text{Vol}, \\ \text{or: } & \overline{\text{R}} = \text{Vol}, \\ \text{or: } & \overline{\text{R}} = \text{Vol}, \\ \\ \text{MATCH} &= \text{Vol} & \text{if: } \underbrace{[\text{AO-A10}]}_{\text{MESET}} \neq \text{DO-D7} + \text{parity}, \\ & \text{with } & \overline{\text{RESET}} = \text{Vol}, \\ & \overline{\text{S}} = \text{Vol}, \text{ and } & \overline{\text{W}} = \text{Vol}, \\ \end{split}$$

#### **FUNCTION TABLE**

|   | 11 | VPUT: | s     | OUTPUT | s  | I/O    | FUNCTION        |

|---|----|-------|-------|--------|----|--------|-----------------|

| w | R  | \$    | RESET | MATCH  | PE | D0-D7  | FUNCTION        |

| Н | L  | L     | Н     | Н      | Н  | Output | Read            |

|   |    |       |       | L      | L  |        | Parity error    |

| н | Н  | Ļ     | н     | L      | Н  | Input  | Not equal       |

|   |    |       |       | н      | L  |        | Undefined error |

| 1 |    |       |       | н      | Н  |        | Equal           |

| L | Х  | L     | н     | Н      | IN | Input  | Write           |

| X | Х  | Н     | н     | Н      | Н  | Hi-Z   | Device disabled |

| Х | Х  | Х     | Ł     | н      | t  | t      | Memory reset    |

<sup>&</sup>lt;sup>†</sup>The state of these pins is dependent on inputs  $\overline{W}$ ,  $\overline{R}$ , and  $\overline{S}$ .

# logic symbol<sup>†</sup>

<sup>&</sup>lt;sup>†</sup>These symbols are in accordance with ANSI/IEEE Std 91-1984

# functional block diagram (positive logic) RESET (1) R (13) EN 8x < 8 RAM 2K×9 A0 (6) 0 A0 (5) A1 (4) A2 (3) A3 (2) A4 (2) COMP A5 (28) $A = \frac{0}{2047}$ A6 (27) (17) MATCH P = Q 8 A7 (26) AB (25) Q. A9 (24) A10 (23) (15) PE 10 2k INPUT EN BUFFERS PARITY D0 (9) D1 (10) D2 (11) D3 (21) D4 (20) 70 CHECKER D5 (20) D6 (19) D7 (18) PARITY <u>s</u> (16) GENERATOR W (14)

# SN74ACT2152A, SN74ACT2154A 2K×8 CACHE ADDRESS COMPARATORS

#### **TERMINAL FUNCTIONS**

| NAME NO.  A0 6 A1 5 A2 4 A3 3 A4 2 A5 28 A6 27 A7 26 A8 25 A9 24 A10 23 D0 9 D1 10 D2 11 D3 12 Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  D5 20 D6 19 D7 18 GND 7.8 Ground  MATCH 17 When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 \( \Omega \text{ minimum} \text{ input} \text{ so driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 \( \Omega \text{ minimum} \text{ input} \text{ so are a to ViL. PE is an open-drain output so an external pull-up resistor of 220 \( \Omega \text{ minimum} \text{ input} \text{ so are a to ViL. PE is an open-drain output so an external pull-up resistor of 220 \( \Omega \text{ minimum} \text{ input} \text{ . Reset input} \text{ . Asynchronously clears entire RAM array to zero and forces MATCH high when \text{ RESET is at ViL. VCC 22 Supply voltage}  W 14 Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when \( \Omega \text{ Sare at ViL} \)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PIN   |     | DESCRIPTION                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | NAME  | NO. | DESCRIPTION                                                                                                                                                            |

| Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Bate of the write cycle.  Data inputs/outputs. Do-D7 are data inputs during the compare and write modes. DO-D7 are data outputs during the read mode.  Data inputs/outputs. DO-D7 are data inputs during the compare and write modes. DO-D7 are data outputs during the read mode.  When MATCH output is at V <sub>OH</sub> during a compare cycle, DO-D7 plus generated parity equals the contents of the 9-bit memory location addressed by AO-A10. MATCH is also driven high during deselect, reset, and read. Since the "ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by AO-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the DO-D7 pins and the MATCH and PE outputs are forced high.  Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  VCC 22 Supply voltage  W tite control input. Writes DO-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                     | A0    | 6   |                                                                                                                                                                        |

| Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Dod 20  Dod 9  Dod 10  Dot input for a data inputs/outputs during the compare and write modes. Do-D7 are data outputs during the read mode.  Dod 19  Dod 19  Dod 19  Dot 18  GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 'AcCT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  PE 15  PARTICLE TO A Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by AO-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IH</sub> .  VCC 22 Supply voltage  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                        | A1    | 5   |                                                                                                                                                                        |

| Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Bate 110  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Data inputs/outputs. Do-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  Data inputs. Do-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during during desides. D0-D7 are data outputs during during desides. D0-D7 and penerated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycle, D0-D7 plus generated parity error in the stored data. During write cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when W and S are at V <sub>IL</sub> .  S 16 Chipselect input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MAT | A2    | 4   |                                                                                                                                                                        |

| Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Address inputs. Addresses 1 of 2048 random access memory locations. Must be stable for the duration of the write cycle.  Do 9  D1 10  D2 11  D3 12  D4 21  D5 20  D6 19  D7 18  GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 \( \Omega \) minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 \( \Omega \) minimum is required.  RESET 1  Reset input. When R and S are at V <sub>IL</sub> and \( \overline{W} \) is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1  Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when \( \overline{R} \) is at V <sub>IH</sub> .  VCC 22 Supply voltage  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when \( \overline{W} \) and \( \overline{S} \) eat at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                           | А3    | 3   |                                                                                                                                                                        |

| A5 28 A6 27 A7 26 A8 25 A9 24 A10 23 D0 9 D1 10 D2 11 D3 12 D4 21 D5 20 D6 19 D7 18 GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH and PE high when S is at V <sub>IL</sub> . S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH high when W and S are at V <sub>IL</sub> . Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> . Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> . Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> . Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A4    | 2   | Addison invested Addisonnes 1 of 2048 condem annexes memory locations. Must be stable for the direction of the write                                                   |

| A6 27 A7 26 A8 25 A9 24 A10 23 D0 9 D1 10 D2 11 D3 12 Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  D5 20 D6 19 D7 18 GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 'Act2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Reset input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  VCC 22 Supply voltage  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A5    | 28  | · ·                                                                                                                                                                    |

| A8 25 A9 24 A10 23 D0 9 D1 10 D2 11 D3 12 D4 21 D5 20 D6 19 D7 18 GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  PE 15 Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH and PE high when R is at V <sub>IH</sub> .  Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH high when R and S are at V <sub>IL</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A6    | 27  | cycle.                                                                                                                                                                 |

| A9 24 A10 23  D0 9 D1 10 D2 11 D3 12 Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  D5 20 D6 19 D7 18 GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Reset input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A7    | 26  |                                                                                                                                                                        |

| Data inputs/outputs. DO-D7 are data inputs during the compare and write modes. DO-D7 are data outputs during the read mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A8    | 25  |                                                                                                                                                                        |

| DO 9 D1 10 D2 11 D3 12 Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  D4 21 D5 20 D6 19 D7 18 GND 7,8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  P6 15 P7 15 P8 20 P8 2                                                       | A9    | 24  |                                                                                                                                                                        |

| D1 10 D2 11 D3 12 Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  D5 20 D6 19 D7 18 GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  P6 15 Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  R6 R8 13 Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IL</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A10   | 23  |                                                                                                                                                                        |

| D2 11 D3 12 D3 12 D4 21 D5 20 D6 19 D7 18  GND 7.8 Ground  MATCH 17 Pairty error input/output. During compare cycle, D0-D7 plus generated parity equals the contents of the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Pairty error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DO    | 9   | · ·                                                                                                                                                                    |

| D3 12 Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during the read mode.  D5 20 D6 19 D7 18  GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Reset input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D1    | 10  |                                                                                                                                                                        |

| D4 21 the read mode.  D5 20 D6 19 D7 18  GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minmum is required.  PE 15 Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D2    | 11  |                                                                                                                                                                        |

| D5 20 D6 19 D7 18 Ground  MATCH 17 When MATCH output is at VOH during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  PE 15 Parity error input/output. During compare cycles, PE at VOL indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  RESET 1 Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D3    | 12  | Data inputs/outputs. D0-D7 are data inputs during the compare and write modes. D0-D7 are data outputs during                                                           |

| D6 D7 18  GND 7.8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D4    | 21  | the read mode.                                                                                                                                                         |

| D7 18  GND 7,8 Ground  When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D5    | 20  |                                                                                                                                                                        |

| GND   7.8   Ground   When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.    Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.    Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.    RESET   1   Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .   S   16   Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .   VCC   22   Supply voltage   Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D6    | 19  |                                                                                                                                                                        |

| When MATCH output is at V <sub>OH</sub> during a compare cycle, D0-D7 plus generated parity equals the contents of the 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage  W Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D7    | 18  |                                                                                                                                                                        |

| MATCH   17   9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.    Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.    Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.    RESET   1   Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .   S   16   Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .   V <sub>CC</sub>   22   Supply voltage   Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GND   | 7,8 |                                                                                                                                                                        |

| 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.  Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage  W Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |     | When MATCH output is at VOH during a compare cycle, D0-D7 plus generated parity equals the contents of the                                                             |

| Parity error input/output. During compare cycles, PE at V <sub>OL</sub> indicates a parity error in the stored data. During write cycles, PE can force a parity error into the 9th-bit location specified by AO-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the DO-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage  W Write control input. Writes DO-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MATCH | 17  | 9-bit memory location addressed by A0-A10. MATCH is also driven high during deselect, reset, and read. Since the                                                       |

| PE 15 cycles, PE can force a parity error into the 9th-bit location specified by A0-A10 when PE is taken to V <sub>IL</sub> . PE is an open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage  W write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |     | 'ACT2154A features an open-drain MATCH output, an external pull-up resistor of 220 Ω minimum is required.                                                              |

| open-drain output so an external pull-up resistor of 220 Ω minimum is required.  Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage  W Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |     | Parity error input/output. During compare cycles, PE at VOL indicates a parity error in the stored data. During write                                                  |

| Read input. When R and S are at V <sub>IL</sub> and W is at V <sub>IH</sub> , addressed data is output to the D0-D7 pins and the MATCH and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  S 16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  VCC 22 Supply voltage  W Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PĒ    | 15  | cycles, $\overline{PE}$ can force a parity error into the 9th-bit location specified by AO-A10 when $\overline{PE}$ is taken to $V_{IL}$ . $\overline{PE}$ is an       |

| A and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  17 VCC 22 Supply voltage  18 Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |     | open-drain output so an external pull-up resistor of 220 $\Omega$ minimum is required.                                                                                 |

| A and PE outputs are forced high.  RESET 1 Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at V <sub>IL</sub> .  16 Chip select input. Enables device when S is at V <sub>IL</sub> . Deselects device and forces MATCH and PE high when S is at V <sub>IH</sub> .  17 VCC 22 Supply voltage  18 Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - E   |     | Read input. When $\overline{R}$ and $\overline{S}$ are at $V_{ I }$ and $\overline{W}$ is at $V_{ H }$ , addressed data is output to the DO-D7 pins and the MATCH      |

| This is a second of the select input. Enables device when \$\overline{S}\$ is at \$V_{ \overline{L}}\$. Deselects device and forces MATCH and \$\overline{PE}\$ high when \$\overline{S}\$ is at \$V_{ \overline{L}}\$. VCC 22 Supply voltage  We write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when \$\overline{W}\$ and \$\overline{S}\$ are at \$V_{ \overline{L}}\$.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R     | 13  |                                                                                                                                                                        |

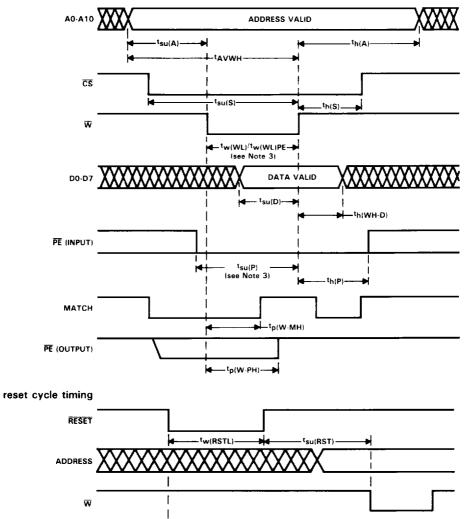

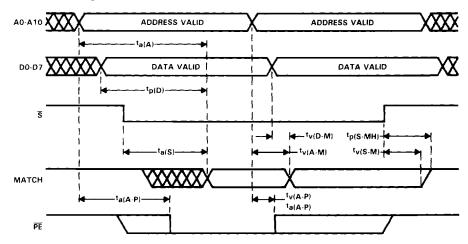

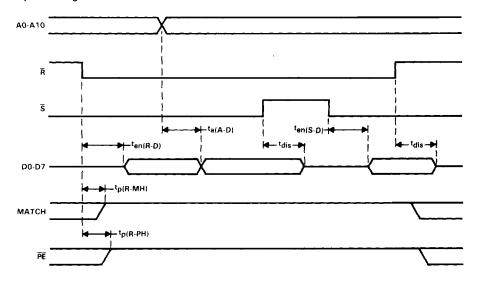

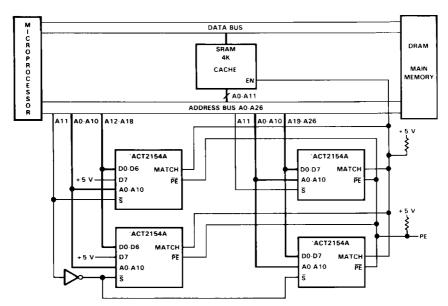

| V <sub>CC</sub> 22 Supply voltage  Write control input. Writes D0-D7 and generated parity into RAM and forces MATCH high when W and S are at V <sub>IL</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RESET | 1   | Reset input. Asynchronously clears entire RAM array to zero and forces MATCH high when RESET is at VIL.                                                                |