# MB8421/8422-90/-90L/-90LL/-12/-12L/-12LL CMOS 16K-BIT DUAL-PORT SRAM

# 2K x 8 Bits CMOS Dual-Port Static Random Access Memory

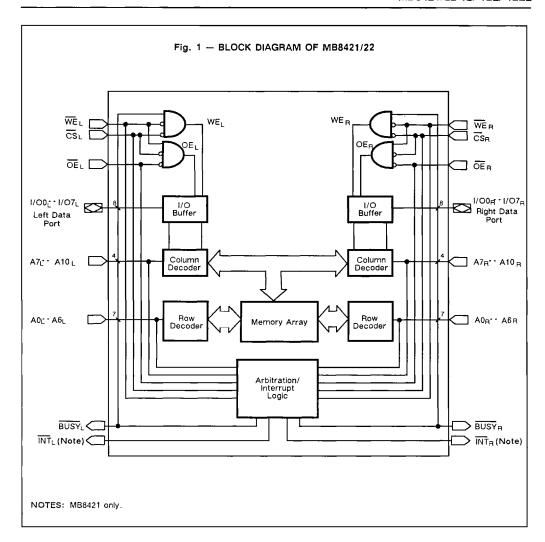

The Fujitsu MB8421 and MB8422 are 2,048 words x 8 bits dual-port high-performance static random access memories (SRAMs) fabricated in CMOS. The SRAMs use asynchronous circuits; thus, no external clocks are required. MB8421 and MB8422 provide the user with two separately controlled I/O ports with independent addresses, Chip Select (CS), Write Enable (WE), Output Enable (OE), and I/O functions. This arrangement permits independent access to any memory location for either a Read or Write operation — a useful feature for shared data processing applications. These devices have an automatic power-down feature controlled by CS.

To avoid data contention on the same address, a BUSY input is provided for address arbitration; in addition, MB8421 utilizes an interrupt (INT) flag which allows communication between systems on either side of the RAM. Both devices use a single +5 V power supply and all pins are TTL-compatible.

Some typical applications for these memory devices are multiprocessing systems, distributed networks, external register files, and peripheral controllers.

Organization: 2.048 words x 8 bits

Static operation: no clocks or timing strobe required

Access time: t<sub>AA</sub> = t<sub>ACS</sub> = 90 ns max. (MB8421/22-90)

(MB8421/22-90L) (MB8421/22/-90LL)

t<sub>AA</sub> = t<sub>ACS</sub> = 120 ns max. (MB8421/22-12)

(MB8421/22-12L) (MB8421/22/-12LL)

· Power consumption for the standard version:

660 mW max. (Both ports active) 385 mW max. (One port active) 38.5 mW max. (Both ports standby, TTL) 11 mW max. (Both ports standby, CMOS)

Power consumption for the L and LL-versions;

495 mW max. (Both ports active) 275 mW max. (One port active) 27.5 mW max. (Both ports standby, TTL) 1.1 mW max. (Both ports standby, CMOS)

- Single +5 V power supply ±10% tolerance

- TTL compatible inputs and outputs

- Three-state outputs with OR-tie capacity

- Electrostatic protection for all inputs and outputs

- Address arbitration function: BUSY flag

- Interrupt function for communication between systems (MB8421 only): INT flag

- Data retention voltage: 2 V min.

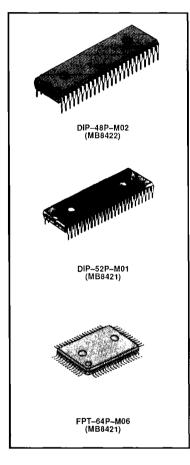

- Standard Plastic Packages:

48-pin DIP MB8422-xx(L/LL)P 52-pin DIP MB8421-xx(L/LL)P 64-pin QFP MB8421-xx(L/LL)PFQ

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Copyright © 1990 by FWITSU LIMITED and Fulltsu Microelectronics, Inc.

#### ABSOLUTE MAXIMUM RATINGS 1, 2

| Parameter                                                     | Designator      | Value                        | Unit |  |

|---------------------------------------------------------------|-----------------|------------------------------|------|--|

| Supply Voltage                                                | V <sub>cc</sub> | ~0.5 to +7                   | ٧    |  |

| Input Voltage on any pin with respect to V <sub>SS</sub>      | VIN             | -0.5 to V <sub>CC</sub> +0.5 | v    |  |

| Output Voltage on any I/O pin with respect to V <sub>SS</sub> | VOUT            | -0.5 to V <sub>CC</sub> +0.5 | V    |  |

| Output Current                                                | IOUT            | ± 20                         | mA   |  |

| Power dissipation                                             | PD              | 1.0                          | w    |  |

| Temperature Under Blas                                        | TBIAS           | -10 to +85                   |      |  |

| Storage Temperature                                           | TSTG            | -40 to +125                  | °c   |  |

#### NOTE:

Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

4

## **I/O CAPACITANCE** ( $T_A = 25$ °C, f = 1 MHz)

| Parameter                    | Symbol | Тур | Max | Unit |

|------------------------------|--------|-----|-----|------|

| Input Capacitance (VIN = 0V) | CIN    |     | 10  | pF   |

| I/O Capacitance (VI/O = 0V)  | CI/O   |     | 10  | pF   |

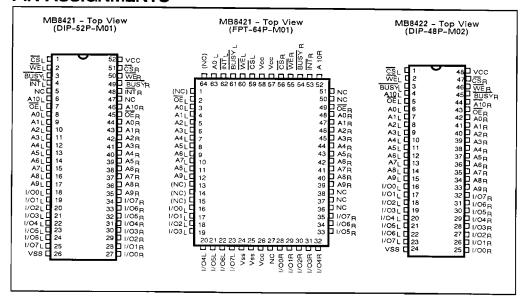

### PIN ASSIGNMENTS

## PIN DESCRIPTIONS

| Left Port | Right Port | Function      | Left Port   | Right Port                                       | Function          |  |

|-----------|------------|---------------|-------------|--------------------------------------------------|-------------------|--|

| WEL       | WER        | Write Enable  | INT,        | ĪNĪB                                             | Interrupt Flag    |  |

| CSL       | CSR        | Chip Select   |             | <del>                                     </del> |                   |  |

| ŌĒL       | ŌĒ R       | Output Enable | A0L A10L    | A0R A10R                                         | Address           |  |

| BUSYL     | BUSYR      | Busy Flag     | 1/00L 1/07L | I/O0R I/O7R                                      | Data Input/Output |  |

|           |            | Vcc           |             |                                                  | Power (Common)    |  |

|           |            | Vss           |             |                                                  | Ground (Common)   |  |

## **FUNCTIONAL OPERATION**

The MB8421 and MB8422 provide two ports with separate control signals, address inputs, and input/output data pins that allow asynchronous read and write operations to any memory location. Each device has an on-chip automatic power-down feature controlled by  $\overline{\text{CS}}$  that places the respective port in the standby mode when the chip is deselected  $\overline{\text{CS}}$  is HiGH).

When a port is enabled, access to the entire memory array is permitted. Each port has an independent Output Enable (OE) control that is active in the read mode and enables the output drivers. Non-contention Read/Write conditions are shown in the following Truth Table; a simplified block diagram of the dual-port SRAM is shown in Fig. 1.

### NON-CONTENTION READ/WRITE CONTROL

| LEFT PO | ORT IN      | PUTS <sup>1</sup> | RIGHT            | PORT IN | IPUTS1 | FL    | AGS   | FUNCTION                               |  |  |

|---------|-------------|-------------------|------------------|---------|--------|-------|-------|----------------------------------------|--|--|

| R/₩L    | <u>CS</u> L | OE <sub>L</sub>   | R/W <sub>R</sub> | CSR     | 0ĒR    | BUSYL | BUSYR | FUNCTION                               |  |  |

| Х       | Н           | Х                 | Х                | Х       | Х      | н     |       | Left Port in Power Down Mode           |  |  |

| Х       | X           | _ x _             | Х                | Ξ       | Х      | н н   |       | Right Port in Power Down Mode          |  |  |

| L       | L           | . X               | Х                | X       | X      | Ξ     | Н     | Data on Left Port Written Into Memory  |  |  |

| Н       | L           | L                 | Х                | Х       | Х      | н н   |       | _ Data in Memory Output on Left Port   |  |  |

| Х       | _ X         | X                 | L                | Ĺ       | X      | н     |       | Data on Right Port Written Into Memory |  |  |

| Х       | Х           | Х                 | Н                | L       | L      | н н   |       | Data in Memory Output on Right Port    |  |  |

#### NOTES:

- 1. A0L-A10L≠ A0R A10R

- 2. H = HIGH, L = LOW, X = Don't Care

### **ARBITRATION LOGIC**

The arbitration logic resolves an address match or chip-enable match and determines the access priority. In both cases, an active  $\overline{\text{BUSY}}$  flag is set for the port-in-waiting. Since both ports are asynchronous, there is the possibility of accessing the same memory location from both sides. In the read mode, this condition is not a problem. However, this is a problem when both ports are in a write mode with different data words or when one port is reading and the other is writing. When both ports access the same memory location, the on-chip arbitration logic determines which port has access and the  $\overline{\text{BUSY}}$  flag for the delayed port is set active LOW and all operations on that port are inhibited. The delayed port can be accessed when the  $\overline{\text{BUSY}}$  flag becomes inactive. Basic modes of abitration are described in subsequent paragraphs.

- When \(\overline{\overline{\sigma}}\) and \(\overline{\sigma}\) are LOW before an address match, on-chip control logic arbitrates between the left and right addresses for device access. Signal states for this condition are shown in the following Truth Table; timing detail is shown under "Data Contention Cycle No. 1 (Address Controlled)."

#### ARBITRATION WITH ADDRESS MATCH BEFORE CS

|      | L   | EFT PO | ORT        |      | R   | IGHT P | ORT                               | FLA   | \GS   | FUNCTION                                                  |

|------|-----|--------|------------|------|-----|--------|-----------------------------------|-------|-------|-----------------------------------------------------------|

| R/WL | CSL | Œ.     | A0 L-A10 L | R/WR | CSR | ĮĒ     | A0 <sub>R</sub> -A10 <sub>R</sub> | BUSYL | BUSYR |                                                           |

| х    | LBR | X      | MATCH      | ×    | L   | X      | MATCH                             | I     | L     | Left Operation Permitted<br>Right Operation Not Permitted |

| x    | L   | X      | MATCH      | Х    | LBL | X      | MATCH                             | L     | Н     | Right Operation Permitted<br>Left Operation Not Permitted |

| Х    | LST | х      | MATCH      | х    | LST | х      | МАТСН                             | Н     | L     | Arbitration Resolved                                      |

NOTES: X = Don't Care, L = Low, H = High, LST= Low Same Time, LBR = Low Before Right, LBL = Low Before Left

#### ADDRESS ARBITRATION WITH CS LOW BEFORE ADDRESS MATCH

|      | L   | EFT PO | ORT      | RIGHT PORT       |     |    | FLAGS                             |       | FUNCTION |                                                           |

|------|-----|--------|----------|------------------|-----|----|-----------------------------------|-------|----------|-----------------------------------------------------------|

| R/WL | CSL | OEL    | A0L-A10L | R/W <sub>R</sub> | CSR | )E | A0 <sub>R</sub> -A10 <sub>R</sub> | BUSYL | BUSYR    | FUNCTION                                                  |

| Х    | L   | Х      | VBR      | ×                | اد  | ×_ | VALID                             | Н     | L        | Left Operation Permitted<br>Right Operation Not Permitted |

| х    | L   | х      | VALID    | Х                | ١   | х  | VBL                               | L     | н        | Right Operation Permitted<br>Left Operation Not Permitted |

| х    | L   | х      | VST      | Х                | L   | х  | VST                               | н     | L        | Arbitration Resolved                                      |

NOTES: X = Don't Care, L = Low, H = High, VST = Valid Same Time, VBR = Valid Before Right, VBL = Valid Before Left

When both  $\overline{\text{CS}}_{\text{L}}$  and  $\overline{\text{CS}}_{\text{R}}$  are low at the same time ( $\overline{\text{CS}}$  controlled) or when both left-and-right addresses are valid at the same time (address controlled), the  $\overline{\text{BUSY}}_{\text{R}}$ flag for the right port is set to the active LOW state and access is granted to the left port.

For the Intel 8086 and Fujitsu's MBL8086 as well as most other microprocessors, the asynchronous  $\overline{\text{BUSY}}$  signal can be directly tied to the READY Input, providing setup-and-hold time requirements are met.

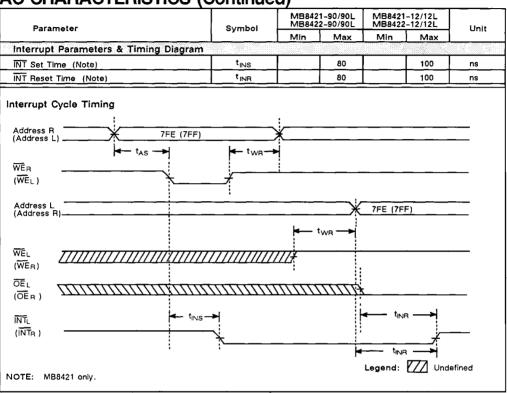

### INTERRUPT FUNCTION

The Interrupt  $\overline{(\text{INT})}$  function provides communication between systems on both sides of the dual-port RAM.  $\overline{\text{INT}}_{L}$  is set LOW when the processor on the right port writes to address 7FE (A0 = L and A1-A10 = H). When the left port acknowledges by reading address 7FE,  $\overline{\text{INT}}_{L}$  is then reset to HIGH. In essence, address 7FE serves as an 8-bit mailbox that transfers information from the right port to the left port. When  $\overline{\text{INT}}_{R}$  is set LOW, the processor on the left port writes to address 7FF (A0-A10=H). When the right port

acknowledges by reading address 7FF,  $\overline{\text{INT}}_{\text{R}}$  is then reset to HIGH. Hence, address 7FF serves as a second 8-bit mailbox, transferring information from the left port to the right port.

On power-up,  $\overline{\text{INT}}_L$  and  $\overline{\text{INT}}_R$  are set to a HIGH state. However, if one port is in the standby mode, the standby port can still be interrupted by the processor on the other port. But if the  $\overline{\text{BUSY}}$  flag is set to the LOW state, the port associated with that flag cannot set or reset the  $\overline{\text{INT}}$  flag.

## RECOMMENDED OPERATING CONDITIONS

(Referenced to Vss)

| Parameter             | Symbol |     | Unit |     |       |  |

|-----------------------|--------|-----|------|-----|-------|--|

| raiameter             | Symbol | Min | Тур  | Max | Offic |  |

| Supply Voltage        | Vcc    | 4.5 | 5.0  | 5.5 | _ ∨   |  |

| Operating Temperature | TA     | 0   |      | 70  | °c    |  |

## DC CHARACTERISTICS

(Recommended Operating Conditions unless otherwise noted.)

| Parameter                                    | Symbol        | Condition                                                                           | MB8421<br>MB8422 |          | MB8421//<br>-90L/-90L | MB8422<br>.L/-12L/-12LL | Unit |

|----------------------------------------------|---------------|-------------------------------------------------------------------------------------|------------------|----------|-----------------------|-------------------------|------|

|                                              |               |                                                                                     | Min              | Max      | Min                   | Max                     |      |

| Operating Supply Current (Both ports Active) | ICC           | Cycle = Min<br>Duty = 100%<br>IOUT = 0 mA                                           |                  | 120      |                       | 90                      | mA   |

|                                              | ISB1          | Both ports at Standby                                                               |                  | 7        |                       | 5                       | mA   |

| Standby<br>Supply Current                    | ISB2          | One port at Standby CSL or CS <sub>R</sub> =VIH, IOUT = 0 mA                        |                  | 70       |                       | 50                      | mA   |

|                                              | ISB3          | Both ports at Full Standby CS <sub>L</sub> & CS <sub>R</sub> ≥ Vcc -0.2V            |                  | 2        |                       | 0.2                     | mA   |

|                                              | ISB4          | One port at Full Standby CS <sub>L</sub> or CS <sub>R</sub> ≥ Vcc -0.2V IOUT = 0 mA |                  | 70       |                       | 50                      | mA   |

| Input Leakage Current                        | ILI           | VIN = 0V to Vcc                                                                     | -10              | 10       | -10                   | 10                      | μΑ   |

| Output Leakage Current                       | ILO           | CS = VIH, VOUT = 0V                                                                 | -10              | 10       | -10                   | 10                      | μА   |

| Input High Voltage                           | VIH           |                                                                                     | 2.2              | Vcc +0.3 | 2.2                   | Vcc +0.3                | ٧    |

| Input Low Voltage                            | VIL           |                                                                                     | -0.3             | 0.8      | -0.3                  | 0.8                     |      |

| Output High Voltage                          | VOH<br>(Note) | IOUT = -1.0 mA                                                                      | 2.4              |          | 2.4                   |                         | ٧    |

| Output Low Voltage                           | VOL           | IOUT = 3.2 mA                                                                       |                  | 0.4_     |                       | 0.4                     | V    |

| Output Low Voltage for<br>Open-Drain         | VOL           | IOUT = 8 mA                                                                         |                  | 0.4      |                       | 0.4                     | ٧    |

NOTE: The BUSY and INT pins require pull-up resistors because they are open-drain outputs.

## **AC CHARACTERISTICS**

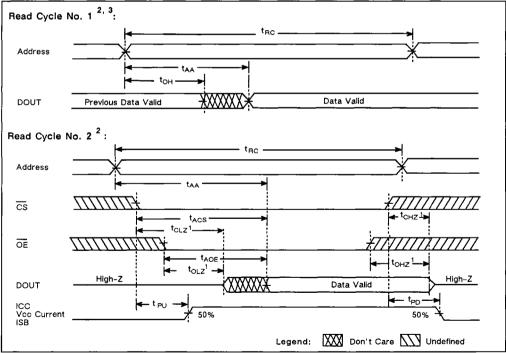

(Recommended Operations Conditions unless otherwise noted.) MB8421-90/90L/90LL MB8422-90/90L/90LL MB8421-12/12L/12LL MB8422-12/12L/12LL Symbol Unit Parameter Min Max Min Max Read Cycle Parameters & Timing Diagrams Read Cycle Time tec 90 120 ns tAA Address Access Time 90 120 ns tACS 90 Chip Select Access Time 120 ns t<sub>AOE</sub> Output Enable Access Time 50 40 ns Output Hold from Address Change ŧон 10 10 ns Chip Select to Output Low-Z (Note 1) t<sub>CLZ</sub> 5 5 ns Output Enable to Output Low-Z (Note 1) torz 5 5 กร Chip Select to Output High-Z (Note 1) t<sub>CHZ</sub> 40 50 ns Output Enable to Output High-Z (Note 1) t<sub>OHZ</sub> 40 50 ns t<sub>PU</sub> 0 Power up from Chip Select ns 0 Power down from Chip Select t<sub>PD</sub> 50 60 ns

#### NOTES:

- 1. Transition is measured at a point of ± 500 mV from steady-state voltage with an output capacitance of 5pF.

- 2. WE is High during read cycle.

- 3. Device is continuously selected (CS = OE = VIL).

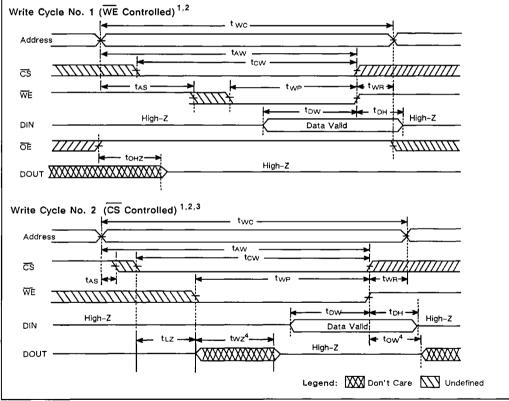

| Parameter                              | Symbol          |     | MB8421-90/90L/90LL<br>MB8422-90/90L/90LL |     | 2/12L/12LL<br>2/12L/12LL | Unit |  |

|----------------------------------------|-----------------|-----|------------------------------------------|-----|--------------------------|------|--|

| r at attletet                          | Symbol .        | Min | Max                                      | Min | Max                      | Onit |  |

| Write Cycle Parameters & Timing Diag   |                 |     |                                          |     | ill Liter 14 Ages        |      |  |

| Write Cycle Time                       | twc             | 90  |                                          | 120 |                          | ns   |  |

| Address Valid to End of Write          | taw             | 85  |                                          | 100 |                          | ns   |  |

| Chip Select to End of Write            | tcw             | 85  |                                          | 100 |                          | ns   |  |

| Address Setup Time                     | tAS             | .0  |                                          | 0   |                          | ns   |  |

| Write Pulse Width                      | t <sub>WP</sub> | 60  |                                          | 70  |                          | ns   |  |

| Write Recovery Time                    | twn             | . 0 |                                          | 0   |                          | ns   |  |

| Data Valid to End of Write             | t <sub>DW</sub> | 40  | 1                                        | 40  |                          | ns   |  |

| Data Hold Time                         | t <sub>DH</sub> | 0   |                                          | 0   |                          | ns   |  |

| Write Enable to Output Low-Z (Note 4)  | t <sub>ow</sub> | 0   | l _                                      | 0   |                          | ns   |  |

| Write Enable to Output High-Z (Note 4) | t <sub>WZ</sub> |     | 40                                       |     | 50                       | ns   |  |

|                                        |                 |     |                                          |     |                          |      |  |

#### NOTES:

- 1. The Write Enable (WE) signal must be high during an address transition.

- If the Output Enable (OE) and Chip Select (CS) signals are in the Read Mode, the associated I/O pins are in the output state; accordingly, input signals of opposite phase must not be applied to the outputs.

- 3. If CS goes high prior to or coincident with the low-to-high transition of WE, the output remains in high-impedance state.

- 4. This parameter is specified at a point + 500 mV from steady-state voltage with an output capacitance of 5 pF.

| Parameter                         | Symbol           |     | 1-90/90L<br>2-90/90L | MB8421<br>MB8422 | Unit |    |  |

|-----------------------------------|------------------|-----|----------------------|------------------|------|----|--|

|                                   |                  | Min | Max                  | Min              | Max  | L  |  |

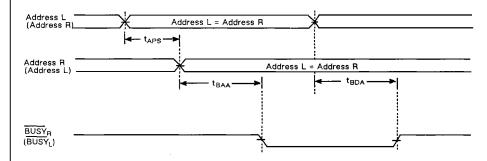

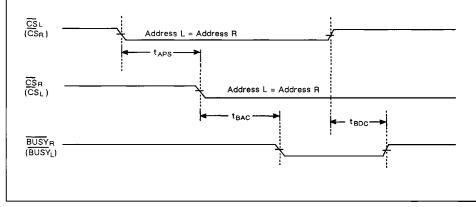

| BUSY Parameters & Data Contention | Timing           |     |                      |                  |      |    |  |

| BUSY Access Time from Address     | t <sub>BAA</sub> |     | 45                   |                  | 60   | ns |  |

| BUSY Output High-Z from Address   | t <sub>BDA</sub> |     | 45                   |                  | 60   | ns |  |

| BUSY Access Time from CS          | t <sub>BAC</sub> |     | 45                   |                  | 60   | ns |  |

| BUSY Output High-Z from CS        | t <sub>BDC</sub> |     | 45                   |                  | 60   | ns |  |

| Arbitration Priority Set up Time  | t <sub>APS</sub> | 20  |                      | 25               |      | ns |  |

Data Contention Cycle No. 1 (Address Controlled)<sup>1, 2</sup>:

Data Contention Cycle No. 2 (CS Controlled)<sup>1, 3</sup>:

#### NOTES:

- 1. In case of dual-access at the same memory location, the port that accesses the RAM first sets the BUSY flag HIGH.

- 2. Chip Select (CS) signal must be low before or coincident with an address transition.

- 3. Address is valid prior to or coincidence with the high-to-low transition of CS.

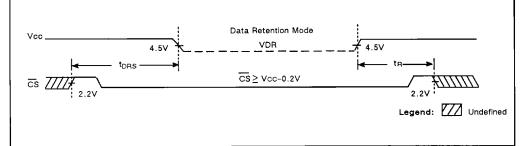

#### DATA RETENTION PARAMETERS & TIMING

| Parameter                            | Symbol         |                 | 1-90/12<br>2-90/12 | MB8421<br>MB8422  | Unit |    |

|--------------------------------------|----------------|-----------------|--------------------|-------------------|------|----|

| rarameter                            | Gymbol         | Min             | Max                | Min               | Max  | 0  |

| Data Retention Parameters & Timing   |                |                 |                    |                   |      |    |

| Data Retention Supply Voltage        | VDR _          | 2.0             | 5.5                | 2.0               | 5.5  | ٧  |

| Data Retention Supply Current (Note) | IDR            |                 | 0.2                |                   | 0.02 | mA |

| Data Retention Setup Time            | tons           | 0               |                    | 0                 |      | ns |

| Operation Recovery Time              | t <sub>R</sub> | t <sub>RC</sub> |                    | t <sub>RC</sub> _ |      | ns |

NOTE: Vcc = VDR = 3V $\overline{CSL} \& \overline{CSR} \ge Vcc - 0.2$

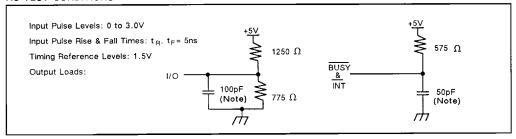

#### AC TEST CONDITIONS

NOTE: Includes jig and stray capacitance.

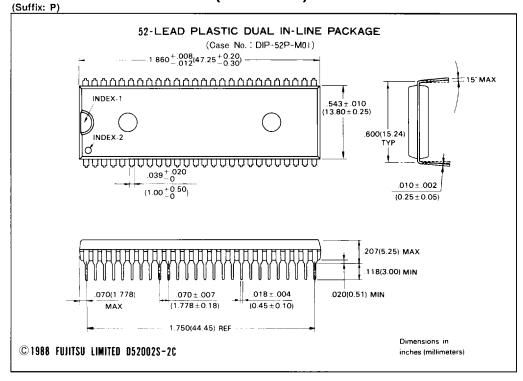

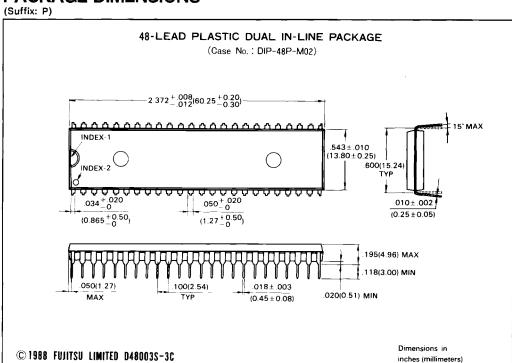

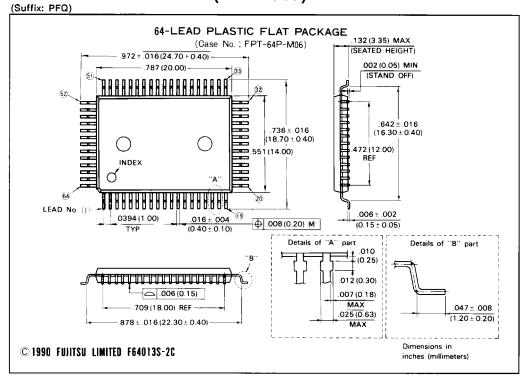

## **PACKAGE DIMENSIONS**

## PACKAGE DIMENSIONS (Continued)

# PACKAGE DIMENSIONS (Continued)