# FT61E14

# **Data Sheet**

# **Key Features**

8-bit EEPROM-based RISC MCU

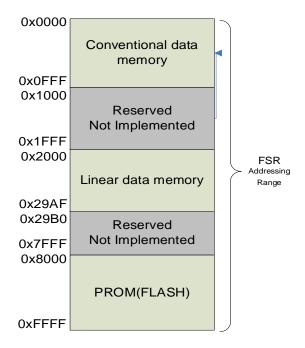

Program: 4k x 14; RAM: 512 x 8; Data: 128 x 8

8 / 10 / 14 / 16 / 20 Pins

12-bit high accuracy ADC (11-bit accuracy at  $V_{ADC-RFF} = 0.5V$ )

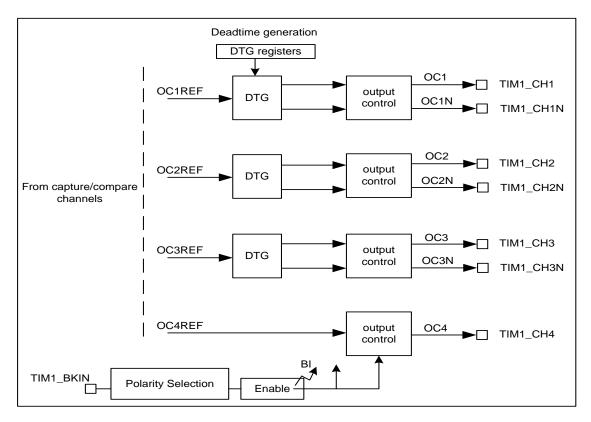

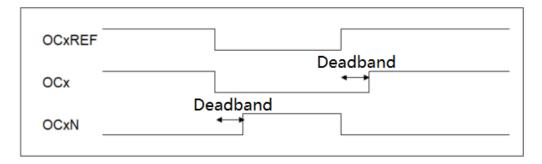

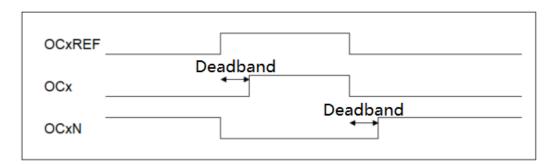

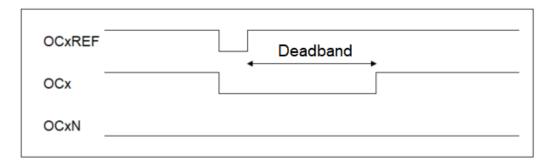

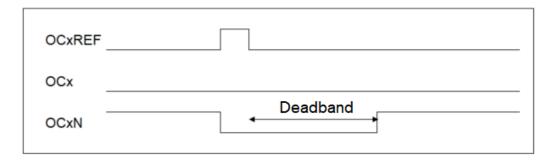

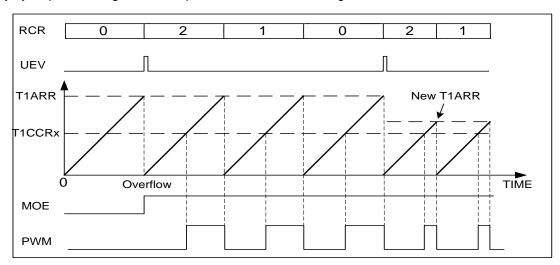

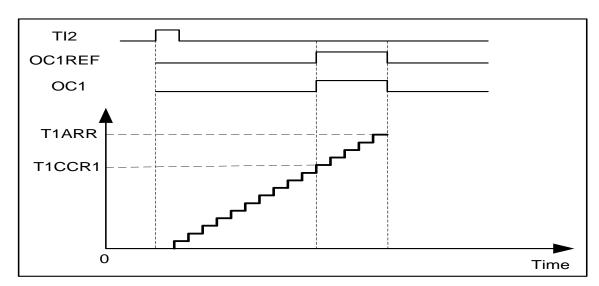

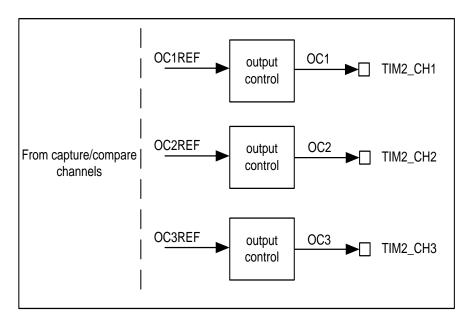

4 Timers, 7 independent PWMs-3 with Deadband

**USART**

Low Standby, WDT and Operating Current

POR, LVR, LVD - Single Input Comparator

Selectable Source and Sink Current

High ESD, High EFT

Low V<sub>DD</sub> Operating Voltage

**Tunable HIRC**

#### 8-bit CPU (EEPROM)

49 RISC instructions: 2T or 4T

16 MHz / 2T (V<sub>DD</sub> ≥ 2.7)

• Up to 20 pins

#### **Memory**

PROGRAM: 4k x 14 (R/W Protect)

DATA: 128 x 8RAM: 512 x 8

• 16-level Hardware Stack

Sector encryption, support IAP

#### Operation Conditions (5V, 25°C)

V<sub>DD</sub> (V<sub>POR</sub> ≤ 1.9V) V<sub>POR</sub> −5.5 V

(Self-regulated by POR, ≤1.7V for above 0°C)

Operation temperature Grade <sup>-</sup>40<sup>-+</sup>85 °C

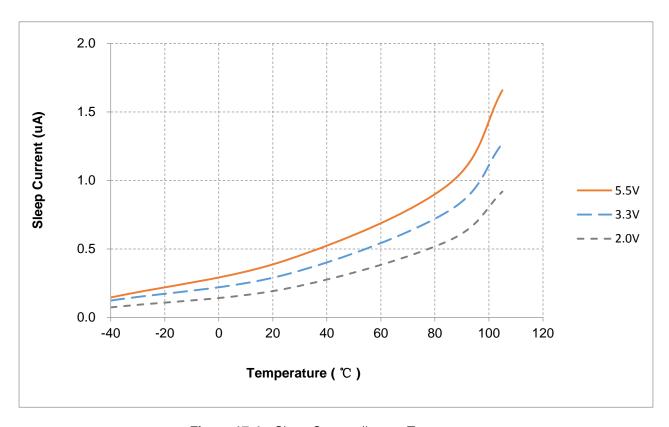

Low Standby 0.4 μA

WDT 3.1 μA

Normal Mode (16 MHz)

286 μA/mips

#### **High Reliability**

100k cycles of erasures (typical)

> 20 years / 85°C storage (typical)

ESD > 7 kV, EFT > 5.5 kV

#### ADC (12-bit)

• 12-bit accuracy (≤ 2 MHz ADC clock)

• 7 + 1 channels

V<sub>ADC-REF</sub>

✓ Internal: 0.5, 2.0, 3.0, V<sub>DD</sub>

✓ External: +,- optional

· Automatic threshold comparison

#### PWM (Total 7)

Support RUN in SLEEP

• 7 capture/compare/PWM channels:

✓ Independent: Duty Cycle, Polarity

• 3 channels (up to 6 I/O):

√ Complementary + Deadband

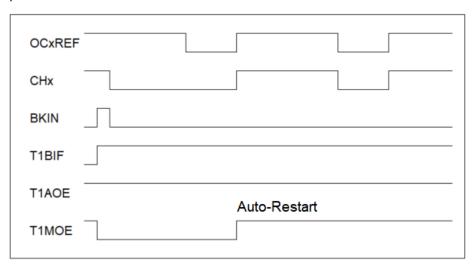

Auto Fault-Breaking (I/O, LVD, ADC)

• Edge-aligned, Center-aligned

One-Pulse mode

#### **Timers**

WDT (16-bit): 3-bit prescaler

Timer1 (16-bit): 16-bit prescaler

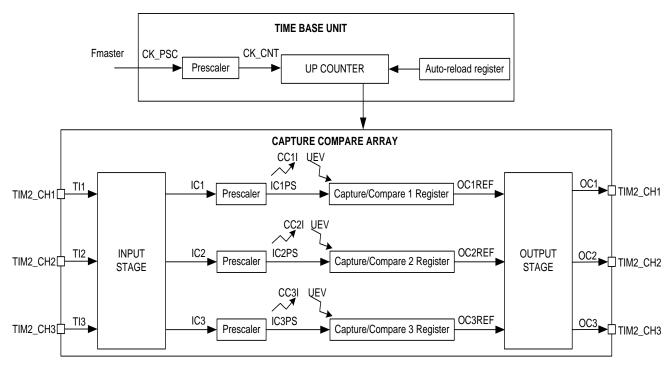

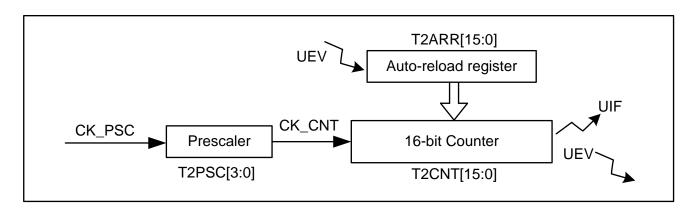

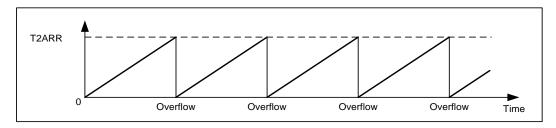

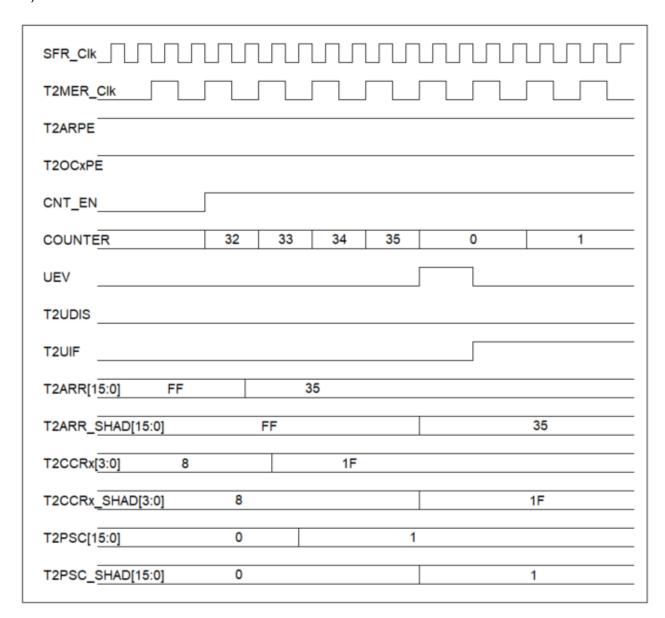

• Timer2 (16-bit): 4-bit prescaler

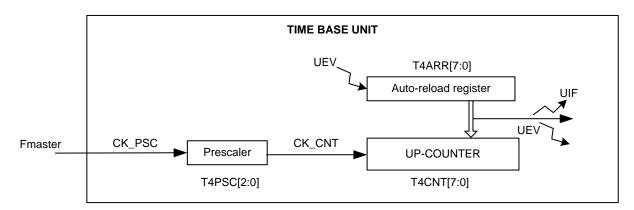

• Timer4 (8-bit): 3-bit prescaler

Auto-reloading

• Support RUN in SLEEP

• Sysclk, LIRC, 1 or 2x {HIRC, Crystal, EC}

#### **Communication Interface**

• USART

#### I/O PORTS (Up to 18 I/O)

• Resistive Pull-Up/Pull-Down

Open-Drain

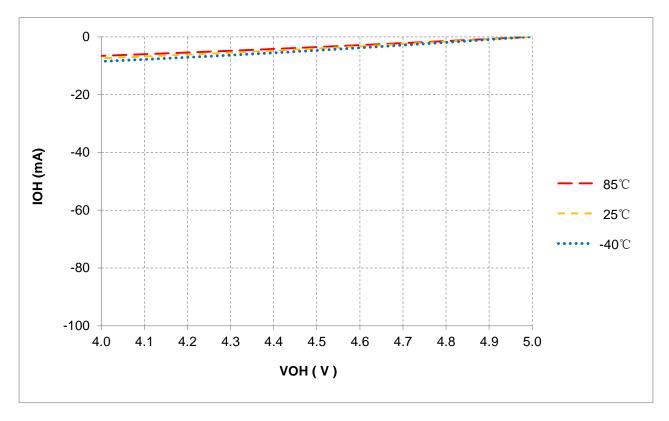

18 I/O I<sub>SOURCE</sub>: 4, 8 or 26 mA (5V, 25°C)

18 I/O I<sub>SINK</sub>: 53 or 62 mA (5V, 25°C)

18 I/O: Interrupt/Wake-Up

#### **Power Management**

SLEEP

• LVR: 2.0, 2.2, 2.5, 2.8, 3.1, 3.6, 4.1 (V)

• LVD: 2.0, 2.4, 2.8, 3.0, 3.6, 4.0 (V) (LVD also functions as a single input comparator with selectable polarity.)

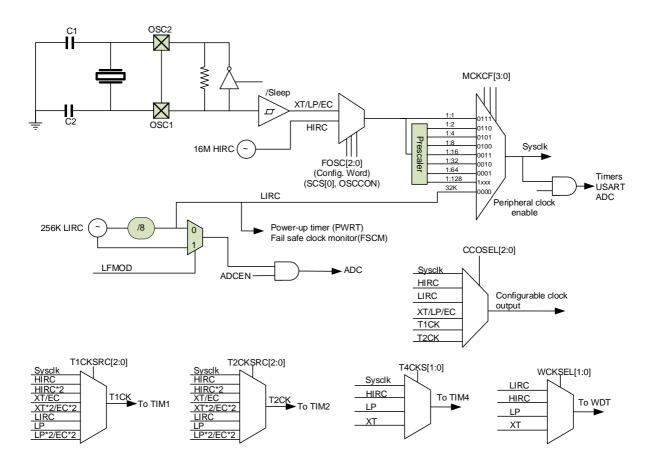

#### System Clock (SysClk)

• HIRC High Speed Internal Oscillator

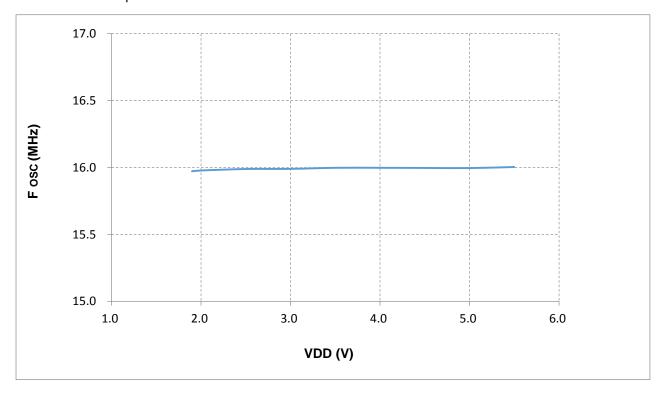

√ 16MHz <±0.5% typical (2.5-5.5V, 25°C)

</p>

✓ Tunable

✓ 1, 2, 4, 8, 16, 32, 64, 128 divider

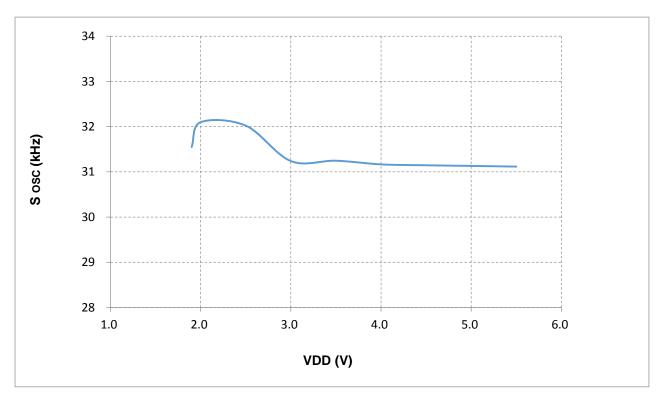

• LIRC Low Power Internal Oscillator

√ 32 kHz or 256 kHz

External Clock (I/O input)

LP/XT crystal input

✓ HIRC or LIRC during startup

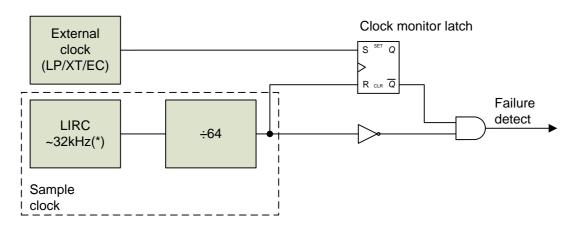

√ Fail-Safe Clock Monitor(FSCM)

#### Other Features (Welecome to enquire)

ADC minimum resolution is 0.12mV, accuracy is 0.24mV, suitable for current detection

½ V<sub>DD</sub> LCD bias

#### **Integrated Development Environment (IDE)**

• On-Chip Debug (OCD), ISP

• 3 hardware breakpoints

• Software-Reset, Stop, Single Step, Skip

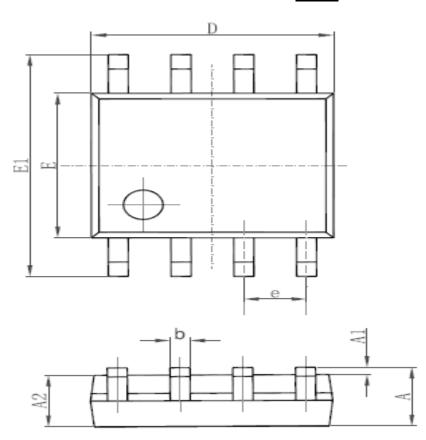

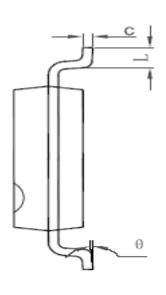

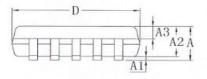

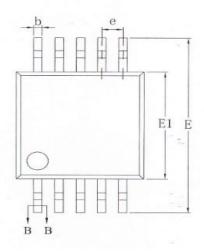

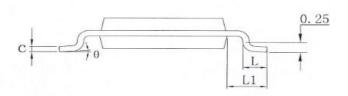

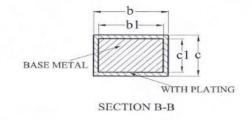

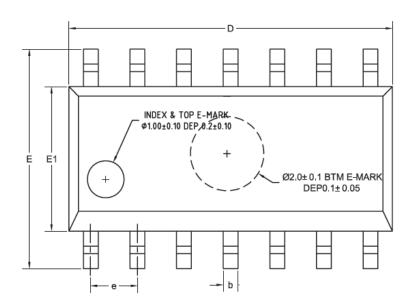

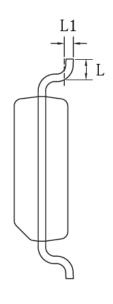

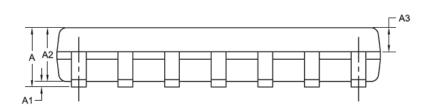

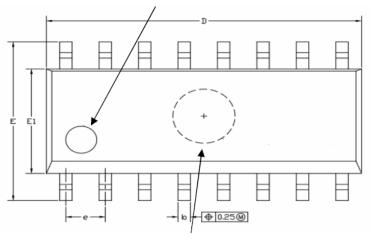

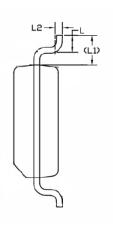

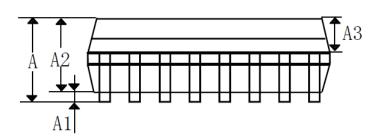

#### **Packages**

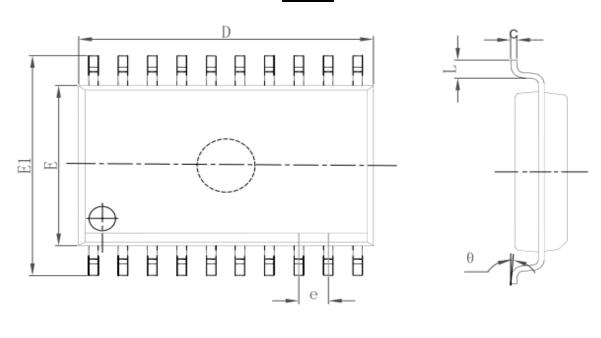

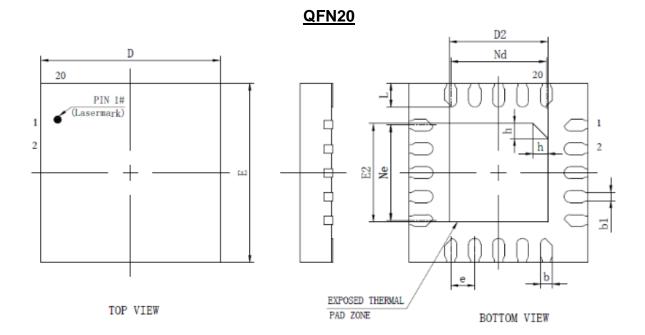

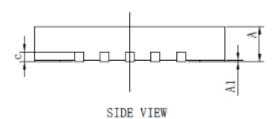

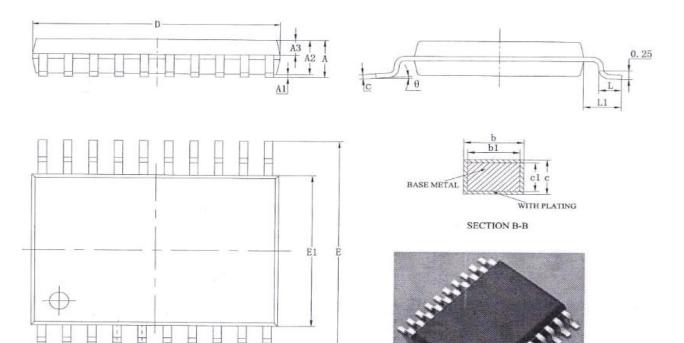

SOP8 MSOP10 SOP14 SOP16

SOP20 TSSOP20 QFN20

Rev1.00 - 1 - 2022-08-25

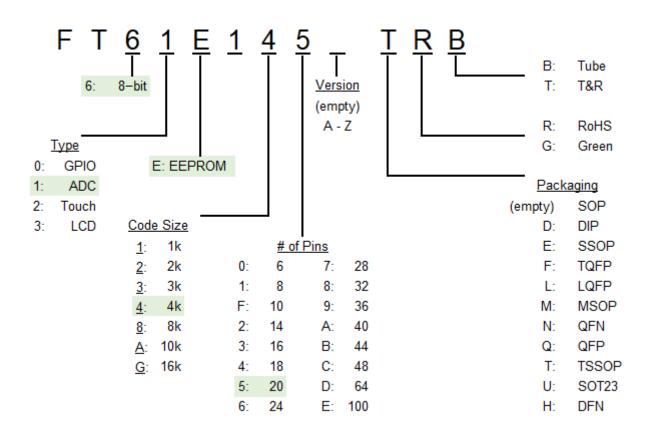

#### PARTS INFORMATION AND SELECTIONS

| Part Number            | Number of I/O | Package |  |  |

|------------------------|---------------|---------|--|--|

| FT61E141- <u>ab</u>    | 6             | SOP8    |  |  |

| FT61E14F- M <u>ab</u>  | 8             | MSOP10  |  |  |

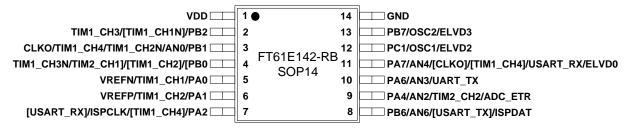

| FT61E142- <u>ab</u>    | 12            | SOP14   |  |  |

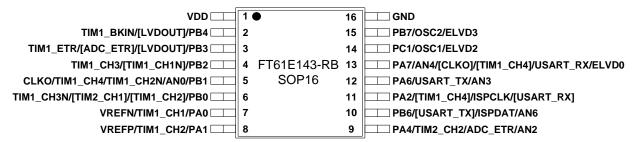

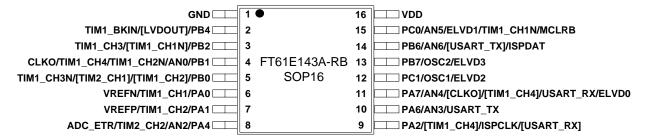

| FT61E143- <u>ab</u>    |               |         |  |  |

| FT61E143A- <u>ab</u>   | 14            | SOP16   |  |  |

| FT61E143B- <u>ab</u>   |               |         |  |  |

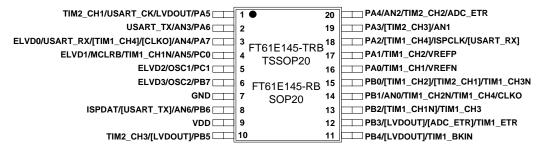

| FT61E145- <u>ab</u>    |               | SOP20   |  |  |

| FT61E145A- <u>ab</u>   |               | 30F20   |  |  |

| FT61E145- T <u>ab</u>  | 40            | TSSOP20 |  |  |

| FT61E145A- T <u>ab</u> | 18            | 1330P20 |  |  |

| FT61E145- Nab          |               | OFNICO  |  |  |

| FT61E145A- N <u>ab</u> |               | QFN20   |  |  |

Where  $\underline{a} = R$ ; RoHS  $\underline{b} = B$ ; Tube = G; Green = T; T&R

MCU Part Number Selections

Rev1.00 - 2 - 2022-08-25

# **Revision History**

| Date       | Revision | Description         |

|------------|----------|---------------------|

| 2022-08-25 | 1.00     | Preliminary version |

Rev1.00 - 3 - 2022-08-25

#### **Table of contents**

| 1. | BLOC   | K DIAGRAM AND PINOUTS                           | 8  |

|----|--------|-------------------------------------------------|----|

|    | 1.1.   | Pinouts                                         | 9  |

|    | 1.2.   | Pin Description by Functions                    | 13 |

| 2. | I/O PC | DRTS                                            | 16 |

|    | 2.1.   | Summary of I/O PORT Related Registers           | 19 |

|    | 2.2.   | Configuring the I/O                             | 23 |

|    | 2.3.   | Pin Out Priority                                | 24 |

| 3. | POWE   | ER-ON-RESET (POR)                               | 26 |

|    | 3.1.   | BOOT Sequence                                   | 26 |

| 4. | SYST   | EM-RESET                                        | 28 |

|    | 4.1.   | Summary of SYSTEM-RESET Related Registers       | 29 |

|    | 4.2.   | Brown-Out Reset (LVR / BOR)                     | 29 |

|    | 4.3.   | Illegal Instruction Reset                       | 30 |

|    | 4.4.   | Software Reset                                  | 30 |

|    | 4.5.   | Stack Overflow/Underflow Reset                  | 30 |

|    | 4.6.   | EMC Reset                                       | 30 |

|    | 4.7.   | Watch Dog Timer (WDT) Reset                     | 30 |

|    | 4.8.   | External I/O System-Reset /MCLRB                | 31 |

|    | 4.9.   | Detect the Type of Last Reset                   | 31 |

| 5. | LOW    | VOLTAGE DETECT / COMPARATOR (LVD)               | 33 |

|    | 5.1.   | Summary of LVD Related Registers                | 34 |

| 6. | OSCIL  | LATORS and SYSCLK                               | 35 |

|    | 6.1.   | Summary of Oscillator Modules Related Registers | 37 |

|    | 6.2.   | Internal Clock Modes (HIRC and LIRC)            | 40 |

|    | 6.3.   | External Clock Modes                            | 42 |

|    |        | 6.3.1. EC mode                                  | 42 |

|    |        | 6.3.2. LP and XT modes                          | 42 |

|    | 6.4.   | HIRC, LIRC and EC inter-switching               | 43 |

| 7. | TIMEF  | RS                                              | 45 |

|     | 7.1.  | Watch I | Dog Timer (WDT)                               | 45  |

|-----|-------|---------|-----------------------------------------------|-----|

|     |       | 7.1.1.  | Summary of WDT Related Registers              | 46  |

|     |       | 7.1.2.  | Configuration and using the WDT               | 47  |

|     | 7.2.  | Advanc  | ced TIMER1                                    | 48  |

|     |       | 7.2.1.  | Summary of Timer1 Related Registers           | 49  |

|     |       | 7.2.2.  | Counting basic units                          | 66  |

|     |       | 7.2.3.  | Clock/Trigger Controller                      | 71  |

|     |       | 7.2.4.  | Capture/Compare Channels                      | 78  |

|     | 7.3.  | Genera  | al-purpose TIMER2                             | 92  |

|     |       | 7.3.1.  | Summary of Timer2 Related Registers           | 93  |

|     |       | 7.3.2.  | Counting basic units                          | 101 |

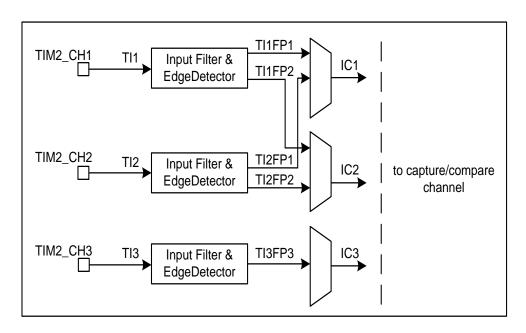

|     |       | 7.3.3.  | Capture / Compare Channel                     | 104 |

|     | 7.4.  | Basic T | TIMER4                                        | 107 |

|     |       | 7.4.1.  | Summary of Timer4 Related Registers           | 108 |

| 8.  | SLEEF | P (POWE | ER-DOWN)                                      | 110 |

|     | 8.1.  | Enter S | SLEEP                                         | 110 |

|     | 8.2.  | Wake L  | Jp from SLEEP                                 | 111 |

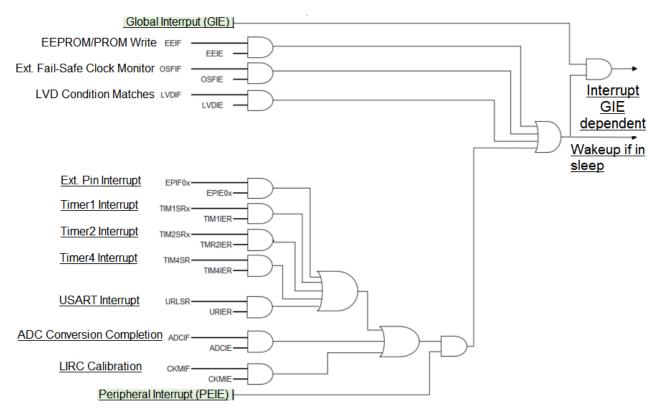

| 9.  | INTER | RUPTS.  |                                               | 113 |

|     | 9.1.  | Summa   | ary of Interrupt Related Registers            | 115 |

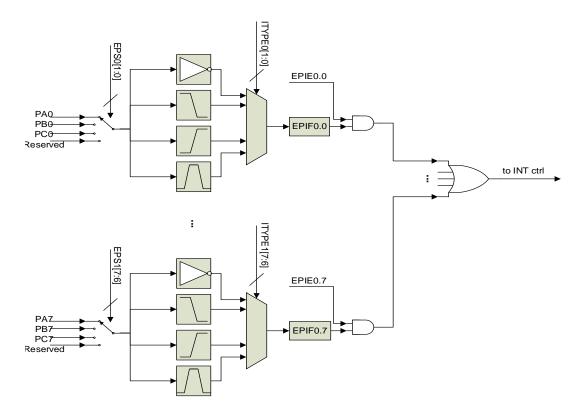

|     | 9.2.  | Externa | al pin interrupt                              | 121 |

| 10. | DATA  | EEPRON  | M AND PROGRAM PROM                            | 122 |

|     | 10.1. | Summa   | ary of DATA EEPROM and PROM Related Registers | 123 |

|     | 10.2. | DATA E  | EEPROM                                        | 124 |

|     |       | 10.2.1. | Writing DATA EEPROM                           | 124 |

|     |       | 10.2.2. | Read DATA EEPROM                              | 126 |

|     | 10.3  | Progran | m PROM                                        | 126 |

|     |       | 10.3.1  | Erase Program PROM                            | 127 |

|     |       | 10.3.2  | Writing Program PROM                          | 128 |

|     |       | 10.3.3  | Reading Program PROM                          | 130 |

|     | 10.4. | Read B  | BOOT Register UCFGx                           | 130 |

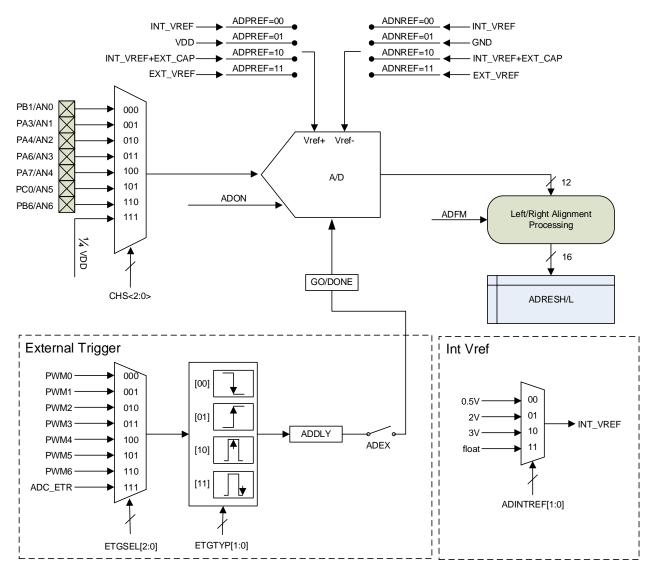

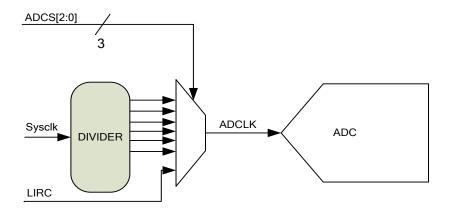

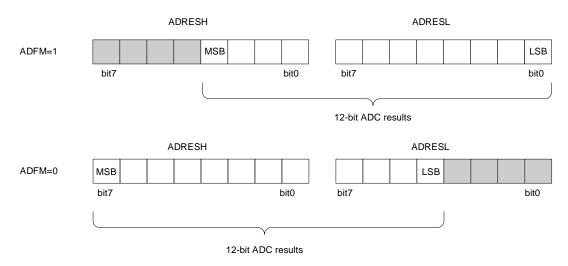

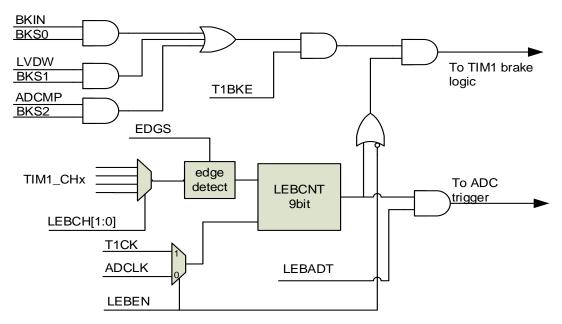

| 11. | 12-bit | ADC      |                                         | 131 |

|-----|--------|----------|-----------------------------------------|-----|

|     | 11.1.  | Summa    | ry of ADC Related Registers             | 132 |

|     | 11.2.  | ADC Co   | onfiguration                            | 136 |

|     |        | 11.2.1.  | ADC Trigger and Configuration of Delay  | 137 |

|     |        | 11.2.2.  | ADC Aborts Conversion                   | 139 |

|     |        | 11.2.3.  | Threshold Comparison                    | 139 |

|     |        | 11.2.4.  | Interrupt                               | 139 |

|     | 11.3.  | Sample   | -and-hold time                          | 140 |

|     | 11.4.  | Minimur  | m sampling time                         | 140 |

|     | 11.5.  | Example  | e of ADC Conversion Steps               | 141 |

| 12. | USAR   | T INTERF | FACE                                    | 144 |

|     | 12.1.  | Summa    | ry of USART Interface Related Registers | 146 |

|     | 12.2.  | USART    | function                                | 152 |

|     |        | 12.2.1.  | Asynchronous Operating Mode             | 152 |

|     |        | 12.2.2.  | Synchronous Operating Mode              | 153 |

|     |        | 12.2.3.  | Infrared Operating Mode                 | 154 |

|     |        | 12.2.4.  | Smart Card Mode                         | 154 |

|     |        | 12.2.5.  | LIN Master Mode                         | 155 |

|     |        | 12.2.6.  | Multiprocessor Communication Mode       | 156 |

|     |        | 12.2.7.  | Automatic baud rate detection           | 156 |

| 13. | МЕМО   | RY REAI  | D / WRITE PROTECTON                     | 158 |

| 14. | SPECI  | AL FUNC  | CTION REGISTERS (SFR)                   | 159 |

|     | 14.1.  | Boot Le  | vel Registers                           | 159 |

|     | 14.2.  | User Re  | egisters                                | 161 |

|     | 14.3.  | STATU    | S Register                              | 173 |

|     | 14.4.  | Stack    |                                         | 174 |

|     | 14.5.  | Indirect | addressing                              | 174 |

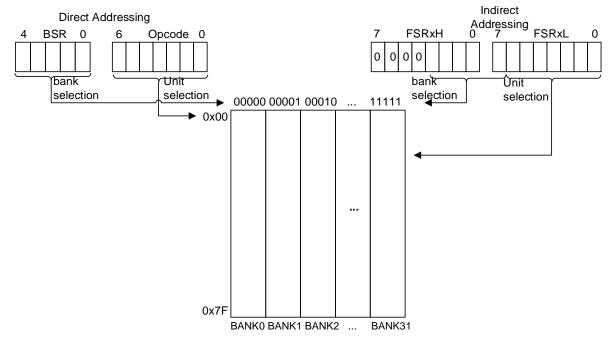

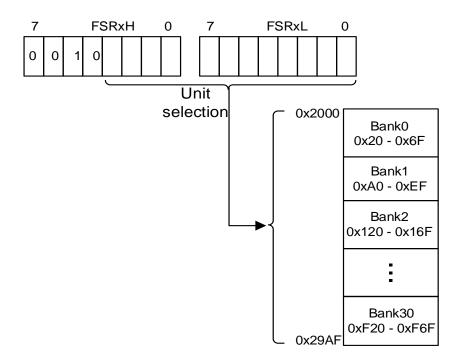

|     |        | 14.5.1.  | Conventional data memory                | 175 |

|     |        | 14.5.2.  | Linear data memory                      | 176 |

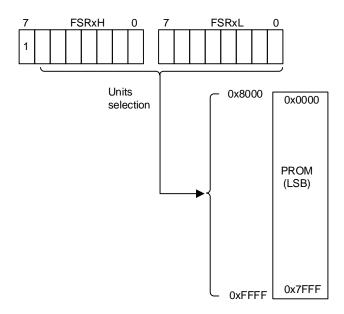

|     |        | 14.5.3.  | Flash program memory                    | 176 |

|     |        |          |                                         |     |

| 15. | INSTR     | UCTION SET                           | . 178 |

|-----|-----------|--------------------------------------|-------|

|     | 15.1.     | Read-Modify-Write (RMW) Instructions | . 180 |

|     | 15.2.     | Instruction details                  | . 181 |

| 16. | ELECT     | RICAL SPECIFICATIONS                 | . 191 |

|     | 16.1.     | Limit Parameters                     | . 191 |

|     | 16.2.     | Operation Characteristics            | . 191 |

|     | 16.3.     | POR, LVR, LVD                        | . 192 |

|     | 16.4.     | I/O PORTS                            | . 193 |

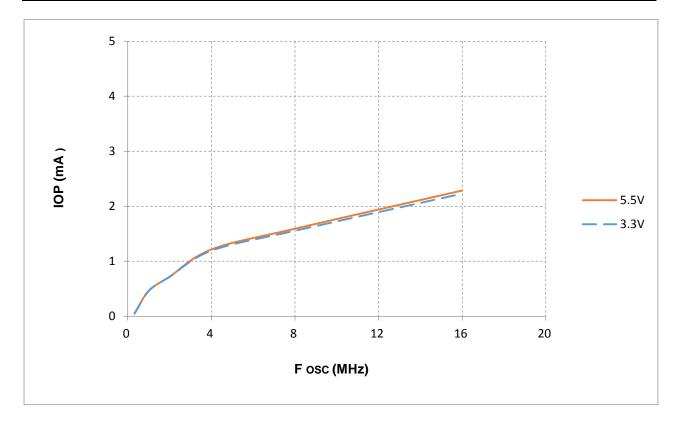

|     | 16.5.     | Operating Current (I <sub>DD</sub> ) | . 193 |

|     | 16.6.     | Internal Oscillators                 | . 194 |

|     | 16.7.     | ADC (12bit) and ADC VREF             | . 194 |

|     | 16.8.     | Program and Data EEPROM              | . 196 |

|     | 16.9.     | EMC characteristics                  | . 196 |

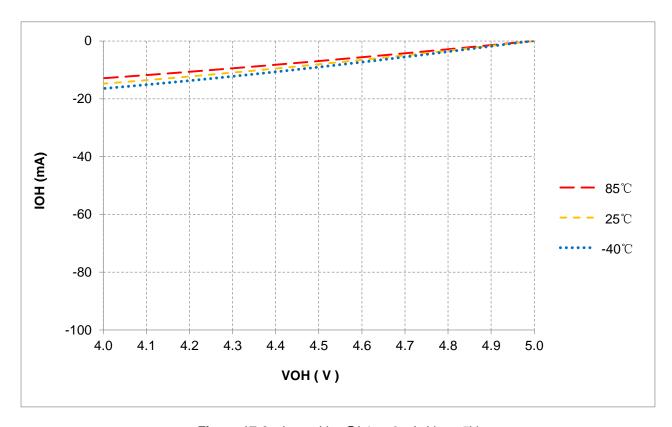

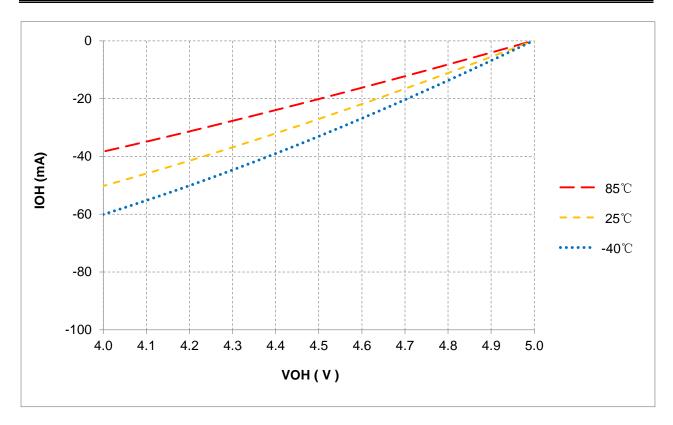

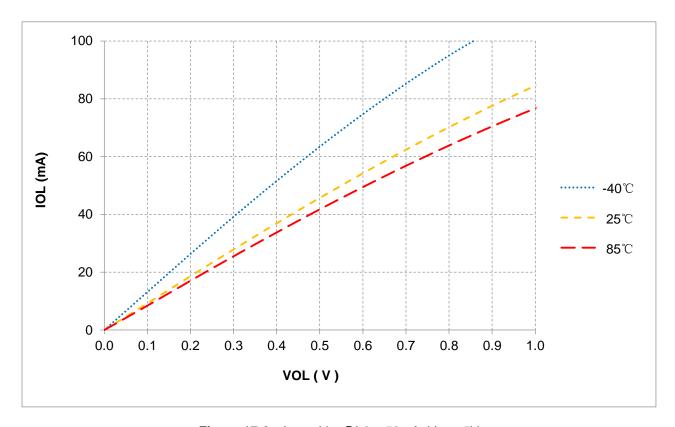

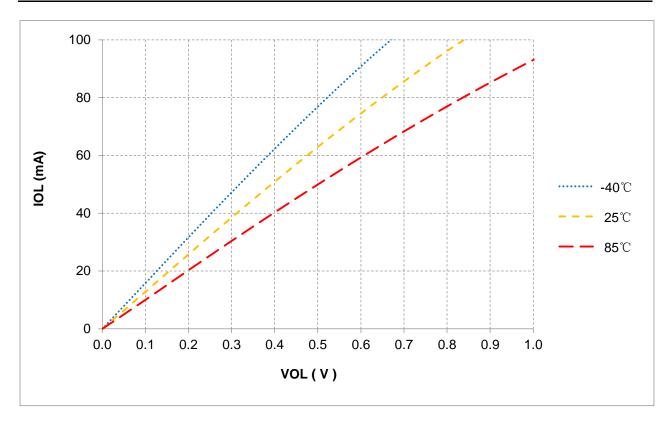

| 17. | Charac    | eterization Graphs                   | . 197 |

| 18. | PACKA     | AGING INFORMATION                    | . 202 |

| 19. | Append    | dix : Register Types                 | . 209 |

| Con | tact Info | ormation                             | . 210 |

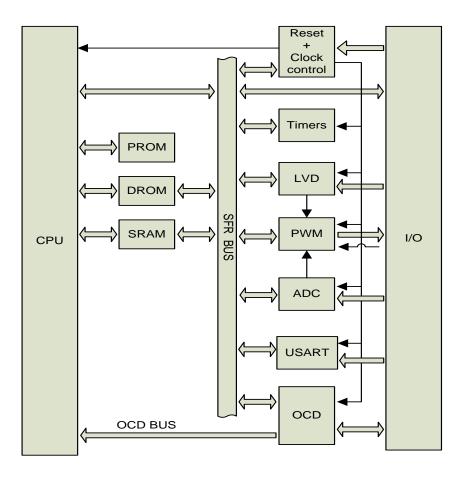

## 1. BLOCK DIAGRAM AND PINOUTS

Figure 1-1 System Block Diagram

The list of standard abbreviations is as follows:

| Abbreviation | Description                                             |

|--------------|---------------------------------------------------------|

| CPU          | Central Processing Unit                                 |

| SFR          | Special Function Registers                              |

| SRAM         | Static Random Access Memory                             |

| DROM         | Data EEPROM                                             |

| PROM         | Program EEPROM                                          |

| Timers       | WDT, Timer1, Timer2, Timer4                             |

| PWM          | Pulse Width Modulator                                   |

| ADC          | Analog to Digital Converter                             |

| LVD          | Low Voltage Detect / comparator                         |

| USART        | Universal Synchronous Asynchronous Receiver Transmitter |

| OCD          | On Chip Debug                                           |

| I/O          | Input / Output                                          |

Rev1.00 - 8 - 2022-08-25

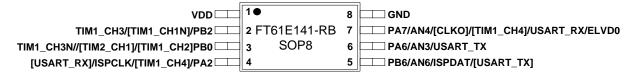

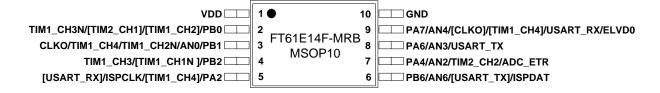

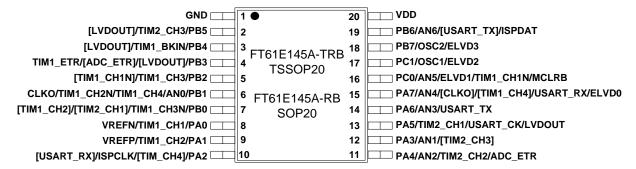

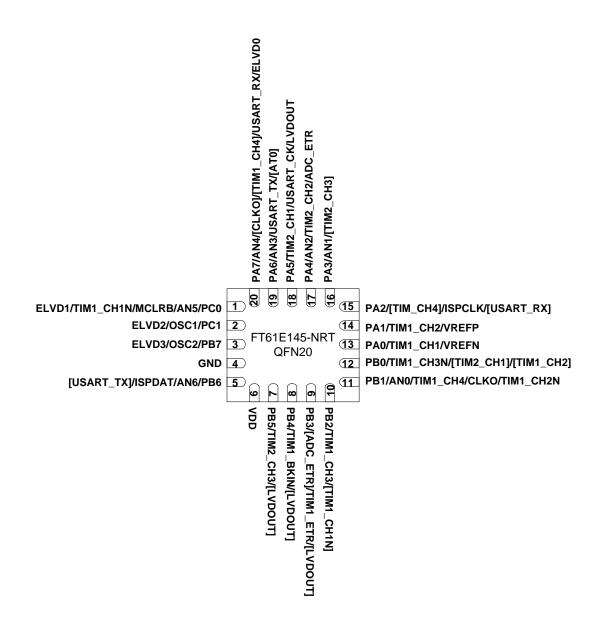

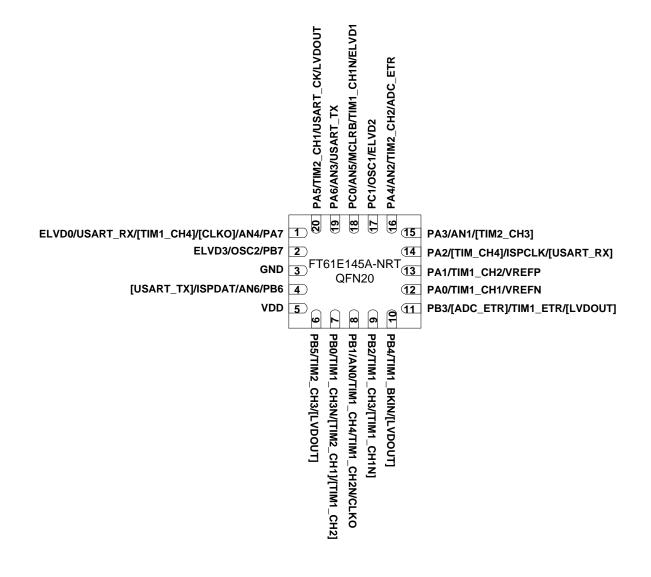

#### 1.1. Pinouts

Figure 1-2 SOP8

Figure 1-3 MSOP10

Figure 1-4 SOP14

Figure 1 -5 SOP16 (A)

Figure 1-6 SOP16 (B)

Rev1.00 - 9 - 2022-08-25

| TIM1_CH3/[TIM1_CH1N]/PB2              | 1 ●            | 16 | PB4/[LVDOUT]/TIM1_BKIN                   |

|---------------------------------------|----------------|----|------------------------------------------|

| CLKO/TIM1_CH4/TIM1_CH2N/AN0/PB1       | 2              | 15 | PB5/[LVDOUT]/TIM2_CH3                    |

| TIM1_CH3N/[TIM2_CH1]/[TIM1_CH2]/PB0 U | 3              | 14 | PB6/AN6/[USART_TX]/ISPDAT                |

| VDD                                   | 4 FT61E143B-RB | 13 | GND GND                                  |

| VREFN/TIM1_CH1/PA0 □□□                | 5 SOP16        | 12 | PB7/OSC2/ELVD3                           |

| VREFP/TIM1_CH2/PA1 □□□                | 6              | 11 | PC1/OSC1/ELVD2                           |

| ADC_ETR/TIM2_CH2/AN2/PA4 C            | 7              | 10 | PA7/AN4/[CLKO]/[TIM1_CH4]/USART_RX/ELVD0 |

| [USART_RX]/ISPCLK/[TIM1_CH4]/PA2 🗆    | 8              | 9  | PA5/LVDOUT/USART_CK/TIM2_CH1             |

**Figure 1 -7** SOP16 (C)

Figure 1-8 TSSOP20 / SOP20 (A)

Figure 1-9 TSSOP20 / SOP20 (B)

Rev1.00 - 10 - 2022-08-25

Figure 1-10 QFN20 (A) 1

Rev1.00 - 11 - 2022-08-25

**Figure 1-11** QFN20 (B) <sup>1</sup>

Rev1.00 - 12 - 2022-08-25

For the QFN20 package, the exposed pad on the bottom is wired to GND.

# 1.2. Pin Description by Functions

| Function       | Description                   | Name     | GPIO   | 8    | 10   | 14   | 16(A) | 16(B) | 16(C) | 20(A) | 20(B) | QFN20    | QFN20    |

|----------------|-------------------------------|----------|--------|------|------|------|-------|-------|-------|-------|-------|----------|----------|

|                |                               |          | equiv. | pins | pins | pins | pins  | pins  | pins  | pins  | pins  | (A) pins | (B) pins |

| Power          |                               | VDD      |        | 1    | 1    | 1    | 1     | 16    | 4     | 9     | 20    | 6        | 5        |

|                |                               | GND      |        | 8    | 10   | 14   | 16    | 1     | 13    | 7     | 1     | 4        | 3        |

|                |                               | PC1      |        |      |      | 12   | 14    | 12    | 11    | 5     | 17    | 2        | 17       |

|                |                               | PC0      |        |      |      |      |       | 15    |       | 4     | 16    | 1        | 18       |

|                |                               | PB7      |        |      |      | 13   | 15    | 13    | 12    | 6     | 18    | 3        | 2        |

|                |                               | PB6      |        | 5    | 6    | 8    | 10    | 14    | 14    | 8     | 19    | 5        | 4        |

|                |                               | PB5      |        |      |      |      |       |       | 15    | 10    | 2     | 7        | 6        |

|                |                               | PB4      |        |      |      |      | 2     | 2     | 16    | 11    | 3     | 8        | 10       |

|                |                               | PB3      |        |      |      |      | 3     |       |       | 12    | 4     | 9        | 11       |

|                | Pull-Up /                     | PB2      |        | 2    | 4    | 2    | 4     | 3     | 1     | 13    | 5     | 10       | 9        |

|                | Pull-Down,                    | PB1      |        |      | 3    | 3    | 5     | 4     | 2     | 14    | 6     | 11       | 8        |

| GPIO           | Digital Input, Digital Output | PB0      |        | 3    | 2    | 4    | 6     | 5     | 3     | 15    | 7     | 12       | 7        |

|                |                               | PA7      |        | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|                |                               | PA6      |        | 6    | 8    | 10   | 12    | 10    |       | 2     | 14    | 19       | 19       |

|                |                               | PA5      |        |      |      |      |       |       | 9     | 1     | 13    | 18       | 20       |

|                |                               | PA4      |        |      | 7    | 9    | 9     | 8     | 7     | 20    | 11    | 17       | 16       |

|                |                               | PA3      |        |      |      |      |       |       |       | 19    | 12    | 16       | 15       |

|                |                               | PA2      |        | 4    | 5    | 7    | 11    | 9     | 8     | 18    | 10    | 15       | 14       |

|                |                               | PA1      |        |      |      | 6    | 8     | 7     | 6     | 17    | 9     | 14       | 13       |

|                |                               | PA0      |        |      |      | 5    | 7     | 6     | 5     | 16    | 8     | 13       | 12       |

| ISP            | ISP-Data                      | ISPDAT   | PB6    | 5    | 6    | 8    | 10    | 14    | 14    | 8     | 19    | 5        | 4        |

| Debugger       | ISP-CLK                       | ISPCLK   | PA2    | 4    | 5    | 7    | 11    | 9     | 8     | 18    | 10    | 15       | 14       |

| External reset | Pull-Up                       | /MCLRB   | PC0    |      |      |      |       | 15    |       | 4     | 16    | 1        | 18       |

|                |                               | ELVD0    | PA7    | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|                | Input                         | ELVD1    | PC0    |      |      |      |       | 15    |       | 4     | 16    | 1        | 18       |

|                | Input                         | ELVD2    | PC1    |      |      | 12   | 14    | 12    | 11    | 5     | 17    | 2        | 17       |

| LVD            |                               | ELVD3    | PB7    |      |      | 13   | 15    | 13    | 12    | 6     | 18    | 3        | 2        |

|                |                               | LVDOUT   | PA5    |      |      |      |       |       | 9     | 1     | 13    | 18       | 20       |

|                | Output                        | [LVDOUT] | PB5    |      |      |      |       |       | 15    | 10    | 2     | 7        | 6        |

|                |                               | [LVDOUT] | PB4    |      |      |      | 2     | 2     | 16    | 11    | 3     | 8        | 10       |

| Function   | Description                 | Name        | GPIO   | 8    | 10   | 14   | 16(A) | 16(B) | 16(C) | 20(A) | 20(B) | QFN20    | QFN20    |

|------------|-----------------------------|-------------|--------|------|------|------|-------|-------|-------|-------|-------|----------|----------|

|            |                             |             | equiv. | pins | pins | pins | pins  | pins  | pins  | pins  | pins  | (A) pins | (B) pins |

|            |                             | [LVDOUT]    | PB3    |      |      |      | 3     |       |       | 12    | 4     | 9        | 11       |

|            | Output                      | CLKO        | PB1    |      | 3    | 3    | 5     | 4     | 2     | 14    | 6     | 11       | 8        |

| Clock      |                             | [CLKO]      | PA7    | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|            | OSC+                        | OSC1        | PC1    |      |      | 12   | 14    | 12    | 11    | 5     | 17    | 2        | 17       |

|            | OSC -                       | OSC2        | PB7    |      |      | 13   | 15    | 13    | 12    | 6     | 18    | 3        | 2        |

|            | PWM1                        | TIM1_CH1    | PA0    |      |      | 5    | 7     | 6     | 5     | 16    | 8     | 13       | 12       |

|            | /PWM1                       | TIM1_CH1N   | PC0    |      |      |      |       | 15    |       | 4     | 16    | 1        | 18       |

|            | /F VVIVII                   | [TIM1_CH1N] | PB2    | 2    | 4    | 2    | 4     | 3     | 1     | 13    | 5     | 10       | 9        |

|            | PWM2                        | TIM1_CH2    | PA1    |      |      | 6    | 8     | 7     | 6     | 17    | 9     | 14       | 13       |

|            | PVVIVIZ                     | [TIM1_CH2]  | PB0    | 3    | 2    | 4    | 6     | 5     | 3     | 15    | 7     | 12       | 7        |

|            | /PWM2                       | TIM1_CH2N   | PB1    |      | 3    | 3    | 5     | 4     | 2     | 14    | 6     | 11       | 8        |

| Timer1     | PWM3                        | TIM1_CH3    | PB2    | 2    | 4    | 2    | 4     | 3     | 1     | 13    | 5     | 10       | 9        |

| (Deadband) | /PWM3                       | TIM1_CH3N   | PB0    | 3    | 2    | 4    | 6     | 5     | 3     | 15    | 7     | 12       | 7        |

|            | PWM4                        | TIM1_CH4    | PB1    |      | 3    | 3    | 5     | 4     | 2     | 14    | 6     | 11       | 8        |

|            |                             | [TIM1_CH4]  | PA7    | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|            | PWM<br>Fault-Break<br>Input | TIM1_BKIN   | PB4    |      |      |      | 2     | 2     | 16    | 11    | 3     | 8        | 10       |

|            | Trigger                     | TIM1_ETR    | PB3    |      |      |      | 3     |       |       | 12    | 4     | 9        | 11       |

|            | 5000                        | TIM2_CH1    | PA5    |      |      |      |       |       | 9     | 1     | 13    | 18       | 20       |

|            | PWM5                        | [TIM2_CH1]  | PB0    | 3    | 2    | 4    | 6     | 5     | 3     | 15    | 7     | 12       | 7        |

| Timer2     | PWM6                        | TIM2_CH2    | PA4    |      | 7    | 9    | 9     | 8     | 7     | 20    | 11    | 17       | 16       |

|            | DIAMAZ                      | TIM2_CH3    | PB5    |      |      |      |       |       | 15    | 10    | 2     | 7        | 6        |

|            | PWM7                        | [TIM2_CH3]  | PA3    |      |      |      |       |       |       | 19    | 12    | 16       | 15       |

|            |                             | AN6         | PB6    | 5    | 6    | 8    | 10    | 14    | 14    | 8     | 19    | 5        | 4        |

|            |                             | AN5         | PC0    |      |      |      |       | 15    |       | 4     | 16    | 1        | 18       |

|            |                             | AN4         | PA7    | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|            | Input                       | AN3         | PA6    | 6    | 8    | 10   | 12    | 10    |       | 2     | 14    | 19       | 19       |

| ADC        |                             | AN2         | PA4    |      | 7    | 9    | 9     | 8     | 7     | 20    | 11    | 17       | 16       |

|            |                             | AN1         | PA3    |      |      |      |       |       |       | 19    | 12    | 16       | 15       |

|            |                             | AN0         | PB1    |      | 3    | 3    | 5     | 4     | 2     | 14    | 6     | 11       | 8        |

|            | <b>.</b>                    | ADC_ETR     | PA4    |      | 7    | 9    | 9     | 8     | 7     | 20    | 11    | 17       | 16       |

|            | Trigger                     | [ADC_ETR]   | PB3    |      |      |      | 3     |       |       | 12    | 4     | 9        | 11       |

Fremont Micro Devices FT61E14x

| Function     | Description                                       | Nama       | GPIO   | 8    | 10   | 14   | 16(A) | 16(B) | 16(C) | 20(A) | 20(B) | QFN20    | QFN20    |

|--------------|---------------------------------------------------|------------|--------|------|------|------|-------|-------|-------|-------|-------|----------|----------|

| Function     | Description                                       | Name       | equiv. | pins | pins | pins | pins  | pins  | pins  | pins  | pins  | (A) pins | (B) pins |

|              | V <sub>REF</sub> -                                | VREFN      | PA0    |      |      | 5    | 7     | 6     | 5     | 16    | 8     | 13       | 12       |

|              | V <sub>REF+</sub>                                 | VREFP      | PA1    |      |      | 6    | 8     | 7     | 6     | 17    | 9     | 14       | 13       |

|              |                                                   | PC1        |        |      |      | 12   | 14    | 12    | 11    | 5     | 17    | 2        | 17       |

|              |                                                   | PC0        |        |      |      |      |       | 15    |       | 4     | 16    | 1        | 18       |

|              |                                                   | PB7        |        |      |      | 13   | 15    | 13    | 12    | 6     | 18    | 3        | 2        |

|              |                                                   | PB6        |        | 5    | 6    | 8    | 10    | 14    | 14    | 8     | 19    | 5        | 4        |

|              |                                                   | PB5        |        |      |      |      |       |       | 15    | 10    | 2     | 7        | 6        |

|              |                                                   | PB4        |        |      |      |      | 2     | 2     | 16    | 11    | 3     | 8        | 10       |

|              |                                                   | PB3        |        |      |      |      | 3     |       |       | 12    | 4     | 9        | 11       |

|              | Low level, Rising edge, Falling edge, Double-edge | PB2        |        | 2    | 4    | 2    | 4     | 3     | 1     | 13    | 5     | 10       | 9        |

| External pin |                                                   | PB1        |        |      | 3    | 3    | 5     | 4     | 2     | 14    | 6     | 11       | 8        |

| interrupt    |                                                   | PB0        |        | 3    | 2    | 4    | 6     | 5     | 3     | 15    | 7     | 12       | 7        |

|              |                                                   | PA7        |        | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|              |                                                   | PA6        |        | 6    | 8    | 10   | 12    | 10    |       | 2     | 14    | 19       | 19       |

|              |                                                   | PA5        |        |      |      |      |       |       | 9     | 1     | 13    | 18       | 20       |

|              |                                                   | PA4        |        |      | 7    | 9    | 9     | 8     | 7     | 20    | 11    | 17       | 16       |

|              |                                                   | PA3        |        |      |      |      |       |       |       | 19    | 12    | 16       | 15       |

|              |                                                   | PA2        |        | 4    | 5    | 7    | 11    | 9     | 8     | 18    | 10    | 15       | 14       |

|              |                                                   | PA1        |        |      |      | 6    | 8     | 7     | 6     | 17    | 9     | 14       | 13       |

|              |                                                   | PA0        |        |      |      | 5    | 7     | 6     | 5     | 16    | 8     | 13       | 12       |

|              | USART_CK                                          | USART_CK   | PA5    |      |      |      |       |       | 9     | 1     | 13    | 18       | 20       |

|              | USART_TX                                          | USART_TX   | PA6    | 6    | 8    | 10   | 12    | 10    |       | 2     | 14    | 19       | 19       |

| USART        | (Open-Drain)                                      | [USART_TX] | PB6    | 5    | 6    | 8    | 10    | 14    | 14    | 8     | 19    | 5        | 4        |

|              | LICART DY                                         | USART_RX   | PA7    | 7    | 9    | 11   | 13    | 11    | 10    | 3     | 15    | 20       | 1        |

|              | USART_RX                                          | [USART_RX] | PA2    | 4    | 5    | 7    | 11    | 9     | 8     | 18    | 10    | 15       | 14       |

Table 1-1

Pin description by functions

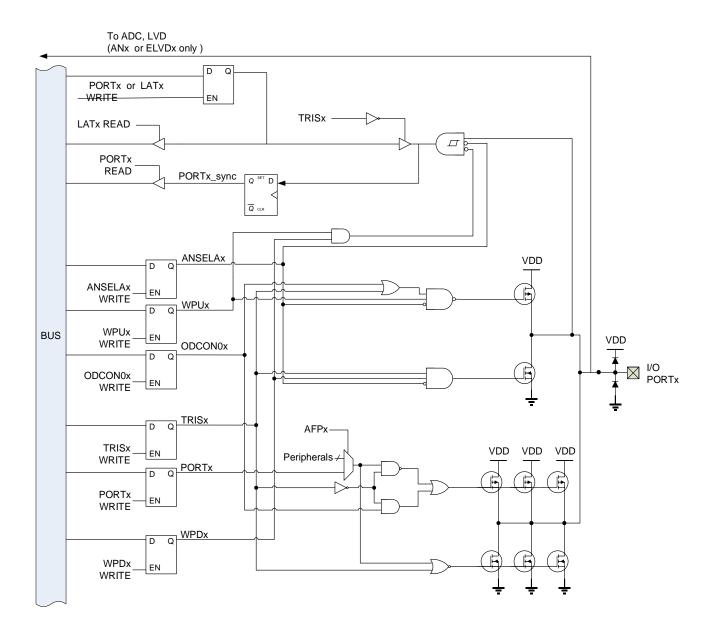

#### 2. I/O PORTS

Up to 18 I/O pins are available depending on the types of package. I/O ports are divided into 3 groups: PORTA (8), PORTB (8) and PORTC (2). **Table 2-1** lists the functions of all I/O pins.

Figure 2-1 PORT Block Diagram

Rev1.00 - 16 - 2022-08-25

All I/O pins have the following functions (Table 2-2, Table 2-3):

**Digital Output**

Weak Pull-Up

Digital Input

- Weak Pull-Down

- Open-Drain (USART corresponding PORTs)

In addition some I/O's have special functions assigned.

- Burn debugger pins (ISP-Data, ISP-CLK) are hardware internal connection and require no set-up.

- The Some special functions are configured at the IDE and loaded during BOOT (Table 2-7):

- External Clock/Crystal Oscillator IN (OSC1, OSC2)

- System-Reset (/MCLRB)

- 3. All other functions are Instruction Level assigned to the various I/O's. They are divided into 4 categories:

- a) Digital Output

- PWM

LVD Output

• GPIO Interrupt-on-Change

ADC trigger (ADC\_ETR)

- Internal Clock Output

- b) Digital Input

- PWM Fault Break

- Timer1 trigger (TIM1\_ETR)

- c) Analog Input

- LVD/BOR

- ADC

- $V_{REF+}$

- d) Communication Interface

- USART

- $V_{\mathsf{REF}}$  -

Rev1.00 - 17 -2022-08-25

Fremont Micro Devices FT61E14x

| Name      | ISP<br>Debugger | CLK    | ADC                  | USART | Interrupt      | LVD      | PWM                         | Digital<br>I/O<br>Pull-Up /<br>Pull-Down | Open-<br>Drain | Source<br>Current<br>(mA) | Sink<br>Current<br>(mA) |

|-----------|-----------------|--------|----------------------|-------|----------------|----------|-----------------------------|------------------------------------------|----------------|---------------------------|-------------------------|

| PA0       |                 |        | (V <sub>REF</sub> -) |       | √              |          | PWM1                        | √                                        |                | 4, 26                     | 53, 62                  |

| PA1       |                 |        | (V <sub>REF</sub> +) |       | √              |          | PWM2                        | √                                        |                | 4, 26                     | 53, 62                  |

| PA2       | CLK             |        |                      | [RX]  | √              |          |                             | √                                        |                | 4, 26                     | 53, 62                  |

| PA3       |                 |        | AN1                  |       | √              |          | [PWM7]                      | √                                        |                | 4, 26                     | 53, 62                  |

| PA4       |                 |        | AN2/<br>Trigger      |       | V              |          | PWM6                        | <b>√</b>                                 |                | 4, 26                     | 53, 62                  |

| PA5       |                 |        |                      | CLK   | √              | LVDOUT   | PWM5                        | √                                        |                | 4, 26                     | 53, 62                  |

| PA6       |                 |        | AN3                  | TX    | √              |          |                             | √                                        | <b>V</b>       | 4, 26                     | 53, 62                  |

| PA7       |                 | Output | AN4                  | RX    | √              | ELVD0    | [PWM4]                      | √                                        |                | 4, 26                     | 53, 62                  |

| PB0       |                 |        |                      |       | V              |          | [PWM2]/<br>PWM3N/<br>[PWM5] | 7                                        |                | 8,26                      | 53, 62                  |

| PB1       |                 | Output | AN0                  |       | V              |          | PWM4/<br>PWM2N              | <b>V</b>                                 |                | 8,26                      | 53, 62                  |

| PB2       |                 |        |                      |       | √              |          | PWM3/<br>[PWM1N]            | <b>V</b>                                 |                | 8,26                      | 53, 62                  |

| PB3       |                 |        | Trigger              |       | $\sqrt{}$      | [LVDOUT] | TIM1_ETR                    | √                                        |                | 8,26                      | 53, 62                  |

| PB4       |                 |        |                      |       | $\checkmark$   | [LVDOUT] | BKIN                        | √                                        |                | 8,26                      | 53, 62                  |

| PB5       |                 |        |                      |       | $\sqrt{}$      | [LVDOUT] | PWM7                        | √                                        |                | 8,26                      | 53, 62                  |

| PB6       | DATA            |        | AN6                  | [TX]  | √              |          |                             | √                                        | $\sqrt{}$      | 8,26                      | 53, 62                  |

| PB7       |                 | OSC-   |                      |       | √              | ELVD3    |                             | √                                        |                | 8,26                      | 53, 62                  |

| PC0       |                 |        | AN5                  |       | √              | ELVD1    | PWM1N                       | √                                        |                | 4, 8, 26                  | 53, 62                  |

| PC1       |                 | OSC+   |                      |       | √              | ELVD2    |                             | √                                        |                | 4, 8, 26                  | 53, 62                  |

| Note<br>s |                 |        |                      |       | /MCLRB<br>=PC0 |          |                             |                                          |                | V <sub>DD</sub> =5, \     | / <sub>DS</sub> =0.5    |

Table 2-1 I/O PORT functions

Note: PORTA and PORTB each has 2 configurable source current levels (see "PSRCAx" and "PSRCBx", Table 2-3), PORTC has 3 configurable source current levels (see "PSRCCx", Table 2-3), All IO each has 2 configurable sink current levels (see "PSINKx", Table 2-3).

## 2.1. Summary of I/O PORT Related Registers

| Name   | Address | bit 7                                    | bit 6                                     | bit 5     | bit 4     | bit 3     | bit 2     | bit 1              | bit 0            | Reset     |

|--------|---------|------------------------------------------|-------------------------------------------|-----------|-----------|-----------|-----------|--------------------|------------------|-----------|

| ANSELA | 0x197   | -                                        | - ANSELA[6:0]                             |           |           |           |           | -000 0000          |                  |           |

| TRISA  | 0x8C    | TRISA                                    | TRISA[7:0], PORTA Data Direction Register |           |           |           | 1111 1111 |                    |                  |           |

| TRISB  | 0x8D    | TRISE                                    | 3[7:0], P                                 | ORTB I    | Data Dir  | ection F  | Register  |                    |                  | 1111 1111 |

| TRISC  | 0x8E    | -                                        | -                                         | -         | -         | -         | -         | PORTC Data Di      | rection Register | 11        |

| PORTA  | 0x0C    | PORT                                     | A Outpu                                   | ıt Regis  | ter       |           |           |                    |                  | XXXX XXXX |

| PORTB  | 0x0D    | PORT                                     | B Outpu                                   | ut Regis  | ster      |           |           |                    |                  | XXXX XXXX |

| PORTC  | 0x0E    | -                                        | -                                         | -         | -         | -         | -         | PORTC Output       | Register         | xx        |

| LATA   | 0x10C   | PORT                                     | A Data I                                  | Latch     |           |           |           |                    |                  | XXXX XXXX |

| LATB   | 0x10D   | PORT                                     | B Data                                    | Latch     |           |           |           |                    |                  | XXXX XXXX |

| LATC   | 0x10E   | -                                        | -                                         | -         | -         | -         | -         | PORTC Data La      | atch             | XX        |

| WPUA   | 0x18C   | PORT                                     | A Weak                                    | Pull-Up   | )         |           | •         |                    |                  | 0000 0000 |

| WPUB   | 0x18D   | PORT                                     | B Weak                                    | Pull-U    | р         |           |           |                    |                  | 0000 0000 |

| WPUC   | 0x18E   | -                                        | -                                         | -         | -         | -         | -         | PORTC Weak F       | Pull-Up          | 00        |

| WPDA   | 0x20C   | PORTA Weak Pull-Down                     |                                           |           |           |           | 0000 0000 |                    |                  |           |

| WPDB   | 0x20D   | PORTB Weak Pull-Down                     |                                           |           |           | 0000 0000 |           |                    |                  |           |

| WPDC   | 0x20E   | -                                        | -                                         | -         | -         | -         | -         | PORTC Weak F       | Pull-Down        | 00        |

| ODCON0 | 0x21F   | -                                        | -                                         | -         | -         | -         | -         | -                  | UROD             | 0         |

| PSRC0  | 0x11A   | PORT                                     | A Sourc                                   | e Curre   | nt Settii | ng        |           |                    |                  | 1111 1111 |

| PSRC1  | 0x11B   | PORT                                     | B Source                                  | ce Curre  | ent Setti | ng        |           |                    |                  | 1111 1111 |

| PSRC2  | 0x11C   | -                                        | -                                         | -         | -         | PORT      | C Sour    | ce Current Setting | l                | 1111      |

| PSINK0 | 0x19A   | PORT                                     | A Sink (                                  | Current   | Setting   | •         |           |                    |                  | 0000 0000 |

| PSINK1 | 0x19B   | PORT                                     | B Sink (                                  | Current   | Setting   |           |           |                    |                  | 0000 0000 |

| PSINK2 | 0x19C   | -                                        | -                                         | -         | -         | -         | -         | PORTC Sink Cu      | irrent Setting   | 00        |

| ITYPE0 | 0x11E   | PORT<br>Setting                          |                                           | x = A, E  | 3, C) ar  | nd POR    | Ty[3:2]   | (y = A, B) Ext. Pi | n Interrupt Type | 0000 0000 |

| ITYPE1 | 0x11F   | PORT                                     | y[7:4] (y                                 | v = A, B) | Ext. Pi   | n Interru | upt Type  | Setting            |                  | 0000 0000 |

| AFP0   | 0x19E   | -                                        | Pin Remapping Register 0 -                |           |           | 00 000-   |           |                    |                  |           |

| AFP1   | 0x19F   | -                                        | Pin Remapping Register 1                  |           |           |           | 00 0000   |                    |                  |           |

| EPS0   | 0x118   | External interrupt EINT3~0 pin selection |                                           |           |           | 0000 0000 |           |                    |                  |           |

| EPS1   | 0x119   | Extern                                   | External interrupt EINT7~4 pin selection  |           |           |           | 0000 0000 |                    |                  |           |

| EPIE0  | 0x94    | Extern                                   | nal pin ir                                | nterrupt  | enable    |           |           |                    |                  | 0000 0000 |

|        | 0x14    | C) d a ma                                | ol nin ir                                 | nterrupt  | flag      |           |           |                    |                  | 0000 0000 |

Table 2-2 Addresses and Reset Values of I/O related registers

| Name              | Status               |                                                 |                        | Register       | Addr.       | Reset        |              |  |

|-------------------|----------------------|-------------------------------------------------|------------------------|----------------|-------------|--------------|--------------|--|

| TRISA             | PORTA                | PORT Digital Output (Direction)                 |                        |                | TRISA[7:0]  | 0x8C         | RW-1111 1111 |  |

| TRISB             | PORTB                | 1 = <u>Disa</u>                                 | <u>lble</u>            |                | TRISB[7:0]  | 0x8D         | RW-1111 1111 |  |

| TRISC             | PORTC                | 0 = Enable (Disable<br>Pull-Up/Down)            |                        |                | TRISC[1:0]  | 0x8E         | RW-11        |  |

|                   | 1 = Disabl           | le Pull-Up                                      | /Down, and [           | Digital Input  |             |              |              |  |

| ANSELA            | (only                | for 7 ADC                                       | channels)              |                | ANSELA[6:0] | 0x197        | RW-000 0000  |  |

|                   | 0 = <u>(No ac</u>    | tion)                                           |                        |                |             |              |              |  |

| WPUA              | PORTA                | Weak P                                          | ull-Up                 |                | WPUA[7:0]   | 0x18C        | RW-0000 0000 |  |

| WPUB              | PORTB                | 1 = Ena                                         | ble                    |                | WPUB[7:0]   | 0x18D        | RW-0000 0000 |  |

| WPUC              | PORTC                | 0 = <u>Disa</u>                                 | <u>ble</u>             |                | WPUC[1:0]   | 0x18E        | RW-00        |  |

| WPDA              | PORTA                | Weak P                                          | ull-Down               |                | WPDA[7:0]   | 0x20C        | RW-0000 0000 |  |

| WPDB              | PORTB                | 1 = Enal                                        | ble                    |                | WPDB[7:0]   | 0x20D        | RW-0000 0000 |  |

| WPDC              | PORTC                | 0 = <u>Disa</u>                                 | <u>lble</u>            |                | WPDC[1:0]   | 0x20E        | RW-00        |  |

| PORTA             | PORTA                | Data Output Register                            |                        |                | PORTA[7:0]  | 0x0C         | RW-xxxx xxxx |  |

| PORTB             | PORTB                | Read: R                                         | eturns V <sub>IO</sub> |                | PORTB[7:0]  | 0x0D         | RW-xxxx xxxx |  |

| PORTC             | PORTC                | Write: Write to the corresponding LATx register |                        |                | PORTC[1:0]  | 0x0E         | RW-xx        |  |

| LATA              | PORTA                |                                                 |                        |                | LATA[7:0]   | 0x10C        | RW-xxxx xxxx |  |

| LATB              | PORTB                | Data Ou                                         | tput latch             | LATB[7:0]      | 0x10D       | RW-xxxx xxxx |              |  |

| LATC              | PORTC                |                                                 |                        |                | LATC[1:0]   | 0x10E        | RW-xx        |  |

|                   | LICART T             | V                                               | Open-Drain             |                |             |              |              |  |

| UROD              | USART_T<br>Open-Drai | 1 = Fnable                                      |                        | ODCON0[0]      | 0x21F       | RW-0         |              |  |

|                   | Opon 214             |                                                 | 0 = <u>Disable</u>     |                |             |              |              |  |

| CLKOS 1           | CLKO                 |                                                 | 1 = <u>PB1</u>         | 0 = PA7        | CKAUX[1]    | 0xF8D        | RW-1         |  |

|                   | TIM1_CH2             | 2                                               | 1 = PB0                | 0 = <u>PA1</u> | AFP0[5]     |              | RW-0         |  |

|                   | TIM2_CH              | 1                                               | 1 = PB0                | 0 = <u>PA5</u> | AFP0[4]     |              | RW-0         |  |

| AFP0 <sup>1</sup> | TIM2_CH3             | 3                                               | 1 = PA3                | 0 = <u>PB5</u> | AFP0[3]     | 0x19E        | RW-0         |  |

|                   | TIM1_CH              | 1N                                              | 1 = PB2                | 0 = <u>PC0</u> | AFP0[2]     |              | RW-0         |  |

|                   | ADC_ETR              |                                                 | 1 = PB3                | 0 = <u>PA4</u> | AFP0[1]     |              | RW-0         |  |

|                   | USART_T              | X                                               | 00 = <u>PA6</u>        | 10 = PA7       | AFP1[5:4]   |              |              |  |

|                   |                      | OUNIT IN                                        |                        | 11 = PA2       | . ,         |              |              |  |

| AFP1 <sup>1</sup> | USART_R              | X                                               | 00 = <u>PA7</u>        | 10 = PA6       | AFP1[3:2]   | 0x19F        | RW-00        |  |

|                   |                      |                                                 | 01 = PA2               | 11 = PB6       |             |              |              |  |

|                   | TIM1_CH4             | <u>4</u>                                        | 00 = <u>PB1</u>        | 10 = PA7       | AFP1[1:0]   |              |              |  |

|                   |                      |                                                 | 01 = PB1               | 11 = PA2       |             |              |              |  |

<sup>&</sup>lt;sup>1</sup> Pin remapping selection.

Fremont Micro Devices FT61E14x

| Name         |         | Status              | Register    | Addr. | Reset        |

|--------------|---------|---------------------|-------------|-------|--------------|

| PSINK0       | PA7-PA0 | Sink Current (mA)   | PSINK0[7:0] | 0x19A | RW-0000 0000 |

| PSINK1       | PB7-PB0 | 1 = 62              | PSINK1[7:0] | 0x19B | RW-0000 0000 |

| PSINK2       | PC1-PC0 | 0 = <u>53</u>       | PSINK2[1:0] | 0x19C | RW-00        |

|              |         | Source Current (mA) |             |       |              |

| PSRCA[7:0]   | PA7-PA0 | 1 = <u>26</u>       | PSRC0[7:0]  | 0x11A | RW-1111 1111 |

|              |         | 0 = 4               |             |       |              |

|              | PB7-PB0 | Source Current (mA) |             |       |              |

| PSRCB[7:0]   |         | 1 = <u>26</u>       | PSRC1[7:0]  | 0x11B | RW-1111 1111 |

|              |         | 0 = 8               |             |       |              |

| PSRCC[3:2]   | PC1     | Source Current (mA) |             |       |              |

| F 31(00[3.2] | FGI     | 11 = <u>26</u>      | PSRC2[3:0]  | 0x11C | RW-1111      |

| PSRCC[1:0]   | PC0     | 01/10 = 8           | FORUZ[3.U]  | UXTIC | 1744 1111    |

| F3NCC[1.0]   |         | 00 = 4              |             |       |              |

Table 2-3

Instruction Level I/O related registers

| Name        |         | Status                       | Register    | Addr. | Reset |

|-------------|---------|------------------------------|-------------|-------|-------|

| ITYPE0[1:0] | PORTx.0 |                              | ITYPE0[1:0] |       | RW-00 |

| ITYPE0[3:2] | PORTx.1 | External interrupt pin EINTx | ITYPE0[3:2] | 0x11E | RW-00 |

| ITYPE0[5:4] | PORTy.2 | trigger type                 | ITYPE0[5:4] | OXIIL | RW-00 |

| ITYPE0[7:6] | PORTy.3 | 00 = <u>Low level</u>        | ITYPE0[7:6] |       | RW-00 |

| ITYPE1[1:0] | PORTy.4 | 01 = Rising edge             | ITYPE1[1:0] |       | RW-00 |

| ITYPE1[3:2] | PORTy.5 | 10 = Falling edge            | ITYPE1[3:2] | 0x11F | RW-00 |

| ITYPE1[5:4] | PORTy.6 | 11 = Double edge             | ITYPE1[5:4] | UXIII | RW-00 |

| ITYPE1[7:6] | PORTy.7 |                              | ITYPE1[7:6] |       | RW-00 |

**Table 2-4** External Pin Interrupt Trigger Type Register (x = A, B, C; y = A, B)

remont Micro Devices FT61E14x

| Name  |                 |          | Status        |               | Register  | Addr.  | Reset |

|-------|-----------------|----------|---------------|---------------|-----------|--------|-------|

| EINT0 | 00 = <u>PA0</u> | 01 = PB0 | 10 = PC0      | 11 = Reserved | EPS0[1:0] |        | RW-00 |

| EINT1 | 00 = <u>PA1</u> | 01 = PB1 | 10 = PC1      | 11 = Reserved | EPS0[3:2] | 0x118  | RW-00 |

| EINT2 | 00 = <u>PA2</u> | 01 = PB2 | 1x = Reserved |               | EPS0[5:4] | OXTTO  | RW-00 |

| EINT3 | 00 = <u>PA3</u> | 01 = PB3 | 1x = Reserved |               | EPS0[7:6] |        | RW-00 |

| EINT4 | 00 = <u>PA4</u> | 01 = PB4 | 1x = Reserved |               | EPS1[1:0] |        | RW-00 |

| EINT5 | 00 = <u>PA5</u> | 01 = PB5 | 1x = Reserved |               | EPS1[3:2] | 0x119  | RW-00 |

| EINT6 | 00 = <u>PA6</u> | 01 = PB6 | 1x = Reserved |               | EPS1[5:4] | 0.1119 | RW-00 |

| EINT7 | 00 = <u>PA7</u> | 01 = PB7 | 1x = Reserved |               | EPS1[7:6] |        | RW-00 |

Table 2-5

External Interrupt Pin Selection Register

| Name                | Statu                       | Register                           | Addr.      | Reset |                |

|---------------------|-----------------------------|------------------------------------|------------|-------|----------------|

| EPIE0x              | External pin interrupt      | 1 = Enable<br>0 = <u>Disable</u>   | EPIE0[7:0] | 0x94  | RW-00000000    |

| EPIF0x <sup>2</sup> | External pin interrupt Flag | 1 = Yes (latched)<br>0 = <u>No</u> | EPIF0[7:0] | 0x14  | R_W1C-00000000 |

Table 2-6 External Pin Interrupt Enable and Flag Registers

| Name  | Function                                          | default  |

|-------|---------------------------------------------------|----------|

| MCLRE | External I/O reset                                | closure  |

|       | LP external oscillator across PC1 (+) and PB7 (-) |          |

| F080  | XT external oscillator across PC1 (+) and PB7 (-) | INTOSCIO |

| FOSC  | EC external oscillator at PC1 (+), PB7 as I/O     | INTOSCIO |

|       | INTOSCIO : PC1 and PB7 as I/O                     |          |

Table 2-7

BOOT Level I/O Related Configuration Registers

Rev1.00 - 22 -

2022-08-25

$<sup>^2</sup>$  Write '1' to clear, and writing '0' has no effect on the bit value. It is recommended to only use the STR and MOVWI instructions for write operations, rather than the BSR instructions .

#### 2.2. Configuring the I/O

For each PORT, configures the following 5 modules according to their functions (Table 2-3):

Digital Output

Weak Pull-Up

Digital Input

Weak Pull-Down

Open-Drain

| Function                              | Digital<br>Input   | Pull-Up /<br>Pull-Down | Digital<br>Output | Settings                                        |

|---------------------------------------|--------------------|------------------------|-------------------|-------------------------------------------------|

| ISP-DATA                              | On                 | Off                    | On                | (Built in hardware, ignore instructions)        |

| ISP-CLK                               | On                 | Off                    | Off               | (Built in hardware, ignore instructions)        |

| /MCLRB                                | On                 | Pull-Up                | Off               | (initialize configuration, ignore instructions) |

| OSC+ (EC)                             | On                 | (optional)             | Off               | (initialize configuration, ignore instructions) |

| OSC+ / OSC-(LP, XT)                   | Off                | Off                    | Off               | (initialize configuration, ignore instructions) |

| ADC                                   | Off                | Off                    | Off               | TRISx = 1; ANSELAx = 1                          |

| LVD                                   | Off <sup>(5)</sup> | Off                    | Off               | TRISx = 1; ANSELAx = 1 (except PC1, PB7)        |

| V <sub>REF+</sub> / V <sub>REF-</sub> | Off                | Off                    | Off               | TRISx = 1                                       |

| ADC trigger                           | On                 | (optional)             | Off               | TRISx = 1                                       |

| USART Input                           | On                 | (optional)             | Off               | TRISx = 1                                       |

| External pin interrupt                | On                 | (optional)             | Off               | TRISx = 1                                       |

| BKIN                                  | On                 | (optional)             | Off               | TRISx = 1                                       |

| Digital Input                         | On                 | (optional)             | Off               | TRISx = 1                                       |

| Clock Output                          | (ignore)           | Off                    | On                | TRISx = 0                                       |

| PWM                                   | On                 | Off                    | On                | TRISx = 0                                       |

| Digital Output                        | On                 | Off                    | On                | TRISx = 0                                       |

| USART Output                          | On                 | Off                    | On                | TRISx = 0                                       |

Table 2-8 Instruction Level I/O Configuration Flags and Registers

#### Note:

- 1. TRISx = 0: "Digital Output" is enabled, "Pull-Up/Pull-Down" is automatically disabled (WPDx, WPUx are ignored).

- 2. TRISx = 1: "Digital Output" is disabled.

- 3. ANSELAx = 1: "Pull-Up", "Pull-Down", "Digital Input" are automatically disabled (WPDx, WPUx are ignored).

- 4. The only instruction that can disable the "Digital Input" is "ANSELAx = 1".

- 5. When a PORT is set as an LVD input, its "Digital Input", "Pull-Up" and "Pull-Down" functions are automatically disabled. When the LVD input needs to be switched between different channels, the "Digital Input" of the currently unselected channel can be disabled by setting "ANSELAx = 1", but PB7 and PC1 are not control by ANSELAx, and the "Digital Input" cannot be disabled, so it should not only be used as LVD input only part of the time.

Rev1.00 - 23 - 2022-08-25

- 6. /MCLR enabled: The Weak Pull-Up function of PC0 is automatically enabled (ignore WPUC[0]); read PORTC[0] as "0".

- 7. Write to the PORTx data output register or the LATx data latch, and the I/O PORT will output the corresponding logic level. Each group of up to 8 I/O data registers share the common address, and the write operation actually performs a "Read-Modify-Write" operation, that is, first read the PORTx latch value (output or input) or LATx of the group data latches, then modified, and finally written back to the PORTx/LATx data registers.

- 8. Digital Output and Digital Input functions can coexist, and some applications require both Digital Output and Digital Input to be enabled.

- 9. ODCON0x = 1: The mapped pins (see "AFP1") selected by "USART\_TX function as open-drain output. The open-drain and internal Pull-Up functions can be turned on at the same time.

- 10. On a full reset or system reset, the PORTx registers will not be reset, but TRISx will be reset to '1', and turn off the output.

For the setting of external pin interrupt, please refer to Section 9 "Interrupts".

#### 2.3. Pin Out Priority

Each I/O pin is multiplexed with multiple functions. When the corresponding module enables the output, the output priority from low to high is shown in **Table 2-9**. Since the inputs are connected to individual function modules, there is no priority issue with the inputs.

| Name | Priority 0 | Priority 1  | Priority 2 | Priority 3 |

|------|------------|-------------|------------|------------|

| PA0  | PA0        | TIM1_CH1    | -          | -          |

| PA1  | PA1        | TIM1_CH2    | -          | -          |

| PA2  | PA2        | [TIM1_CH4]  | ISPCLK     |            |

| PA3  | PA3        | [TIM1_CH3]  | -          | -          |

| PA4  | PA4        | TIM2_CH2    | -          | -          |

| PA5  | PA5        | LVDOUT      | USART_CK   | TIM2_CH1   |

| PA6  | PA6        | USART_TX    | -          | -          |

| PA7  | PA7        | [CLKO]      | [TIM1_CH4] | -          |

| PB0  | PB0        | [TIM1_CH2]  | [TIM2_CH1] | TIM1_CH3N  |

| PB1  | PB1        | TIM1_CH2N   | TIM1_CH4   | CLKO       |

| PB2  | PB2        | [TIM1_CH1N] | TIM1_CH3   | -          |

| PB3  | PB3        | [LVDOUT]    | -          | -          |

| PB4  | PB4        | [LVDOUT]    | -          | -          |

| PB5  | PB5        | [LVDOUT]    | TIM2_CH3   | -          |

| PB6  | PB6        | [USART_TX]  | ISPDAT     | -          |

| PB7  | PB7        | OSC2        |            |            |

| PC0  | PC0        | TIM1_CH1N   | MCLRB      | -          |

| PC1  | PC1        | OSC1        | _          | -          |

**Table 2-9** PinOut Priority

For VerA chips, the precautions are as follows:

- The mapping pin PB0 of TIM1\_CH2 can only be used as PWM output and comparison output, rather than capture input;

- 2. When TIM1\_CH2 output is enabled (T1CC2E=1), if AFP0[5] selects PB0, then PA1 is still occupied by TIM1\_CH2 function and can be used as input rather than GPIO output;

- 3. When TIM2\_CH1 output is enabled (T2CC1E=1), if AFP0[4] selects PA5, then PB0 is still occupied by TIM2\_CH1 function and can be used as input rather than TIM1\_CH2 output or GPIO output.

For chips ≥ VerB, the above restrictions are not applicable.

Rev1.00 - 25 - 2022-08-25

#### 3. POWER-ON-RESET (POR)

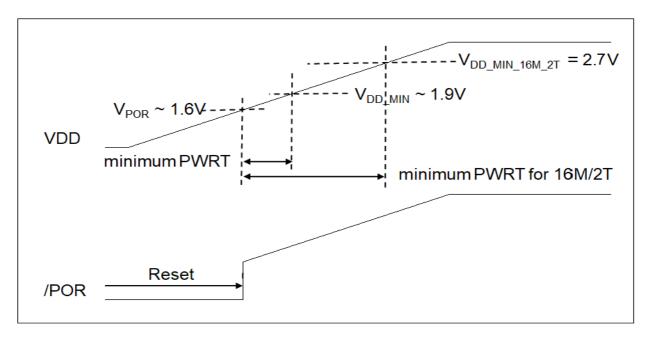

During Power-On,  $V_{DD}$  increases from below the Power-On-Reset Voltage ( $V_{POR}$ ) to above  $V_{POR}$ .  $V_{DD}$  may not have completely discharged to 0V when the CPU is Power-On again.

- 1. The CPU is in a Full-Reset state when  $V_{DD}$  is below  $V_{POR}$ .

- a. All calibrated configuration registers are not reset. Special Function Registers (SFR) are in Reset, except INDFx, Z, DC, C, FSRxL/H, BSREG, WREG, PORTx, LATx, OSCTUNE, EEDATL, EEDATH, EECON2 and SRAM (see Section 14 "Special Function Registers"). Registers not reset, such as SRAM, will hold their values until V<sub>DD</sub> drops below 0.6V (typical). Data of those resisters with V<sub>DD</sub> below 0.6V are undetermined.

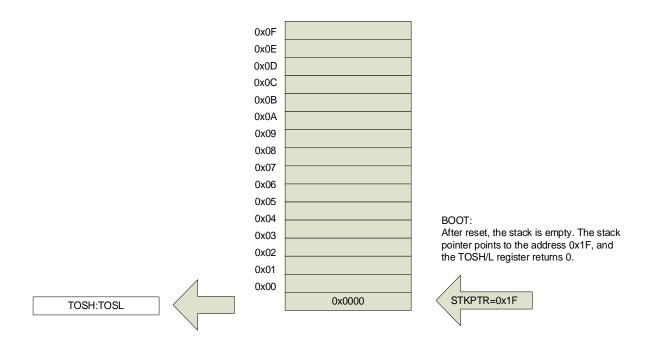

- b. Program Counter = 0x00, Instruction Register = "NOP", Stack Pointer = "TOS" (Top of Stack).

- 2. BOOT commences when V<sub>DD</sub> raises above V<sub>POR</sub>.

- 3. Instruction execution begins with Program Counter = 0x00 after BOOT completion.

$V_{POR}$  is ~1.6V at 25°C (typical), increasing to ~1.9V at -40°C. For  $V_{DD} \ge V_{POR}$ , the CPU can function at a reduced speed of 8 MHz / 2T, which giving an automatically adjusted  $V_{DD}$  operating range according to the temperature change. This is important for battery-powered system as the CPU can function down even to ~1.6V at typical battery operating environments, greatly extending useful battery life.

#### Notes:

- 1. V<sub>POR</sub> is not configurable.

- 2. The POR circuit is always on and will perform a Power-On-Reset any time when  $V_{DD}$  voltage is below  $V_{POR}$ , not just during Power-On.

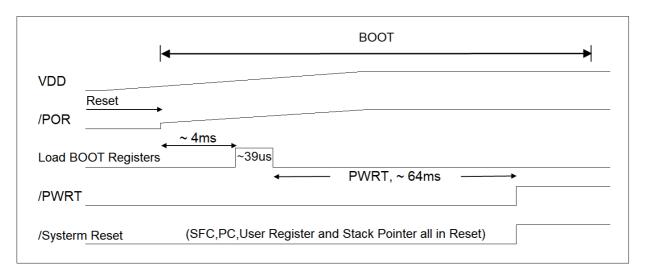

#### 3.1. BOOT Sequence

| Name   | Functions                                              | default  |

|--------|--------------------------------------------------------|----------|

| PWRTEB | Power-Up-Timer, additional ~64ms delay after BOOT load | disabled |

Table 3-1 BOOT configurations

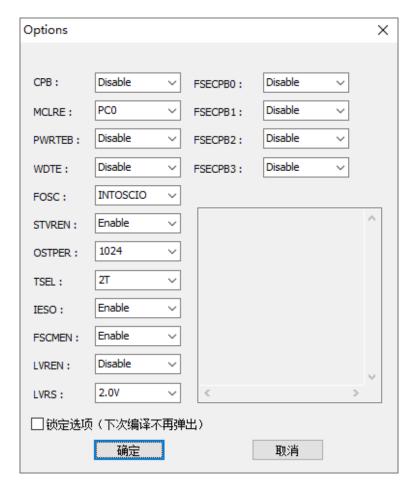

The BOOT configuration is as above. Their values are set at the IDE, not by instructions. during BOOT:

- 1. CPU idles for ~4ms.

- 2. The BOOT Level registers are loaded from the non-volatile memory. It takes ~39us. These registers are pre-set at the IDE and not affected by instructions.

- 3. If Power-On-Timer (PWRT) is enabled, the CPU will idle for ~64ms.

Rev1.00 - 26 - 2022-08-25

Figure 3-1 Power-On Sequence (PWRT enabled)

Figure 3-2 Minimum PWRT time required for power-on process

$V_{DD}$  must be higher than 2.7V by the end of BOOT if the CPU is to run at 16MHz / 2T. The total BOOT time can increase from ~4ms to ~68ms by enabling the PWRT, giving more time for the power system to stabilize.

Enable LVR with  $V_{BOR} \ge 2.7V$  for operation at 16MHz / 2T. In addition, the frequency of LVR enable can be controlled by instruction to monitor  $V_{DD}$  sporadically, instead of always on (see "LVREN", "SLVREN") to reduce power consumption.

#### Notes:

- 1.  $V_{DD}$  should not rise too slowly.  $C_{VDD} \ge 22 \mu F$  is discouraged.

- 2.  $V_{DD}$  capacitor of 1 to  $10\mu F$  is preferred.  $C_{VDD}$  <  $1\mu F$  capacitor may be too small for EFT considerations.

- 3. If a delay in startup is acceptable, enables PWRT to improve CPU stability.

Rev1.00 - 27 - 2022-08-25

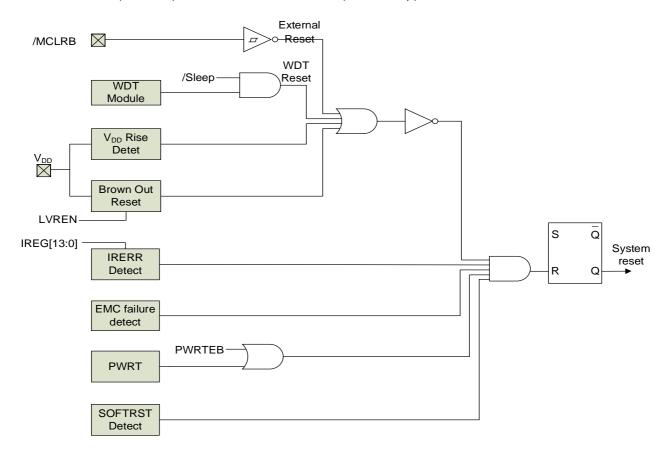

#### 4. SYSTEM-RESET

System-Reset differs from POR in that it is not a Full-Reset. Depending on the trigger type and configurations, CPU may or may not BOOT. BOOT will wait ~4ms, reload the BOOT registers, and further delay system start by ~64ms if PWRT is enabled. In a System-Reset:

- Registers reset during POR will also be reset during system reset, except BOOT registers.

- Program Counter = 0x00, Instruction Register = "NOP", Stack Pointer = "TOS" (Top of Stack).

The following 7 events besides debugger OCD can be configured to trigger a System-Reset:

- 1. Brown-Out (BOR / LVR) always BOOT.

- 2. Illegal Instructions Reset.

- 3. Watch-Dog Reset (WDT, CPU not in SLEEP).

- 4. EMC Reset always BOOT.

- 5. Software Reset (execute instruction "RESET").

- 6. Stack Overflow/Underflow Reset.

- 7. External I/O (/MCLRB) BOOT if "MRBTE" is set. (≥ VerB chip).

Figure 4-1 Reset circuit Block Diagram

#### 4.1. Summary of SYSTEM-RESET Related Registers

Most settings for System-Reset are configured at the IDE, and cannot be changed by instructions.

| Name   | Function                                                                                                                   | default        |

|--------|----------------------------------------------------------------------------------------------------------------------------|----------------|

| STVREN | Stack Overflow/Underflow Reset.  • Enabled  • Disabled                                                                     | enabled        |

| LVRS   | 7 V <sub>BOR</sub> Voltage levels (V):         2.0       / 2.2       / 2.5       / 2.8       / 3.1       / 3.6       / 4.1 | 2.0            |

| LVREN  | LVR  Enabled  Disabled  Enabled except in SLEEP  Instruction controlled (SLVREN)                                           | disabled       |

| WDTE   | <ul> <li>WDT</li> <li>Enabled (Instructions can not be disabled)</li> <li>Instruction controlled (SWDTEN)</li> </ul>       | SWDTEN control |

| MCLRE  | Reset by External I/O                                                                                                      | disabled       |

Table 4-1 BOOT Level RESET related configurations

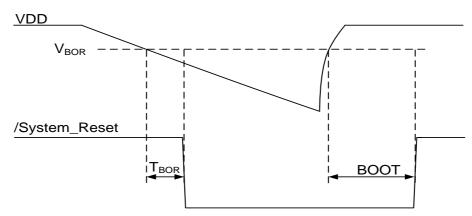

#### 4.2. Brown-Out Reset (LVR / BOR)

Brown-Out occurs when  $V_{DD}$  falls below a pre-configured Brown-Out Voltage ( $V_{BOR}$ ) for a time longer than  $T_{BOR}$ .  $T_{BOR}$  takes 3 to 4 LIRC clock cycles (~94 – 125µs, LIRC will turn on automatically if not already). CPU System-Reset as long as  $V_{DD} \le V_{BOR}$ . Once  $V_{DD} > V_{BOR}$  CPU will BOOT. The /BORF will be set to 0.

While  $V_{POR}$  is fixed,  $V_{BOR}$  can be set to 2.0, 2.2, 2.5, 2.8, 3.1, 3.6, 4.1V (see "LVRS" in Table 4-1).

Figure 4-2 LVR BOOT Timing Diagram

LVR function can have four different settings configured (see "LVREN" in Table 4-1).

#### 1. LVR enabled.

Rev1.00 - 29 - 2022-08-25

Fremont Micro Devices FT61E14x

- 2. LVR disabled.

- 3. LVR enabled, except in SLEEP.

- 4. Let instructions enable or disable LVR (SLVREN, see Table 4-2).

Note: LVR can be instructions disabled in SLEEP to reduce power consumption. The CPU should wake up and enable LVR periodically to monitor  $V_{DD}$  if system  $V_{DD}$  is unstable.

| Name                | Status                                             | Register   | Addr. | Reset |

|---------------------|----------------------------------------------------|------------|-------|-------|

|                     | Only applicable to LVREN configured to control LVR |            |       |       |

| SLVREN <sup>1</sup> | by the SLVREN                                      | LVDCON0[7] | 0x199 | RW-0  |

|                     | 1 = Enable LVR 0 = <u>Disable LVR</u>              |            |       |       |

Table 4-2 Instruction Level LVR registers

#### 4.3. Illegal Instruction Reset

There are many reasons for CPU fetch instruction errors, and the most common reasons are interference and  $V_{DD}$  instability.

Although there is no dedicated Reset instruction, any deliberate illegal instruction is equivalent to a Reset instruction. BOOT after an Illegal Instruction and the Flag IERRF will be set to 1.

#### 4.4. Software Reset

When the program executes Software Reset instruction "RESET", a system reset is generated and the flag /SRSTF will be set to 0.

#### 4.5. Stack Overflow/Underflow Reset

The Stack Overflow or Underflow Reset (by configuring "STVREN") will trigger a System-Reset, and the Overflow Flag STKOVF or Underflow Flag STKUNF will be set to 1.

#### 4.6. EMC Reset

The EMC detection module is always on. When some kind of EMC interference occurs, System-Reset and BOOT generate, and the Flag EMCF will be set to 1.

#### 4.7. Watch Dog Timer (WDT) Reset

WDT overflows during SLEEP will result in a Wake-Up.

In normal mode (not SLEEP mode), a WDT overflow will trigger a System-Reset. And WDT reset can be used to reset a hung CPU. Clear WDT from time to time in the program to avoid false reset.

For details on WDT operation and setting see Section 7.1 Watch Dog Timer (WDT).

Rev1.00 - 30 - 2022-08-25

<sup>&</sup>lt;sup>1</sup>This bit will not be cleared when a Brown-out Reset occurs. Other resets will clear this bit.

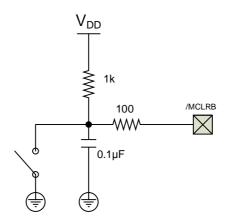

#### 4.8. External I/O System-Reset /MCLRB

The CPU can be reset by a low voltage applied to the /MCLRB (PC0) pin if so configured by BOOT. The /MCLRB pin is usually weak pullup to  $V_{DD}$  with a resistor instead of directly, as shown in **Figure 4-3**. The external RC network also provides glitches filtering and over-current protection.

For ≥ VerB chips, BOOT after a /MCLR System-Reset.

Figure 4-3 /MCLRB reset circuit

#### 4.9. Detect the Type of Last Reset

Eight status flags in the PCON register and the different combinations of Time Out (/TO) and Power Down (/PD) can trace the type of last System-Reset. /BORF should be set to 1 by instructions, and will be latches to "0" after the Reset.

| Name                | Stat                        | Register                                               | Addr.   | Reset |       |

|---------------------|-----------------------------|--------------------------------------------------------|---------|-------|-------|

| STKOVF <sup>2</sup> | Stack Overflows Flag        |                                                        | PCON[7] |       | RW0-0 |

| STKUNF <sup>2</sup> | Stack Underflows<br>Flag    | 1 = Yes                                                | PCON[6] |       | RW0-0 |

| EMCF <sup>2</sup>   | EMC Reset Flag              | 0 = No, or cleared                                     | PCON[5] |       | RW0-0 |

| IERRF <sup>2</sup>  | Illegal Instruction<br>Flag |                                                        | PCON[4] | 0x96  | RW0-0 |

| /MCLRR <sup>3</sup> | External Reset Flag         |                                                        | PCON[3] | 0,30  | RW1-1 |

| /SRSTF <sup>3</sup> | Software Reset Flag         | 1 = <u>No</u> (Software<br>set 1)<br>0 = Yes (latched) | PCON[2] |       | RW1-1 |

| /PORF <sup>3</sup>  | Power-On-Reset<br>Flag      |                                                        | PCON[1] |       | RW1-0 |

| /BORF <sup>3</sup>  | Low-voltage Reset<br>Flag   | ,                                                      | PCON[0] |       | RW1-x |

Table 4-3 Reset Flag Register

Rev1.00 - 31 - 2022-08-25

Write '0' to clear, and writing '1' has no effect on the bit value.

Only '1' can be written, and writing '0' has no effect on the bit value..

Fremont Micro Devices FT61E14x

| Reset Source                             | STKOVF  | STKUNF  | EMCF    | IERRR   | /MCLRR  | /SRSTF  | /PORF                     | /BORF   | /TO       | /PD       |

|------------------------------------------|---------|---------|---------|---------|---------|---------|---------------------------|---------|-----------|-----------|

|                                          | PCON[7] | PCON[6] | PCON[5] | PCON[4] | PCON[3] | PCON[2] | PCON[1]                   | PCON[0] | STATUS[4] | STATUS[3] |

|                                          | 0x96    |         |         |         |         |         | Bank First address + 0x03 |         |           |           |

| POR                                      | 0       | 0       | 0       | 0       | 1       | 1       | 0                         | 1       | 1         | 1         |

| LVR                                      | 0       | 0       | 0       | 0       | 1       | 1       | 1                         | 0       | -         | -         |

| CLRWDT Instructions                      | -       | -       | -       | -       | -       | -       | -                         | -       | 1         | 1         |

| SLEEP Instructions                       | -       | -       | -       | -       | -       | -       | -                         | -       | 1         | 0         |

| WDT overflows while not in SLEEP (Reset) | -       | -       | -       | -       | -       | -       | -                         | -       | 0         | -         |

| WDT overflows while in SLEEP (Wake up)   | -       | -       | -       | -       | -       | -       | -                         | -       | 0         | 0         |

| Software Reset                           | -       | -       | -       | -       | -       | 0       | -                         | -       | -         | _         |

| MCLR Reset (≥ verB)                      | 0       | 0       | 0       | 0       | 1       | 1       | 0                         | 1       | 1         | 1         |

| MCLR Reset (< verB)                      | -       | -       | -       | -       | 0       | -       | ,-                        | -       | -         | -         |

| Illegal Instruction Reset                | -       | -       | -       | 1       | -       | -       | -                         | -       | -         | -         |

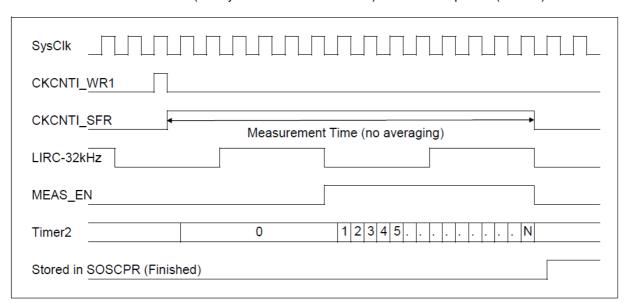

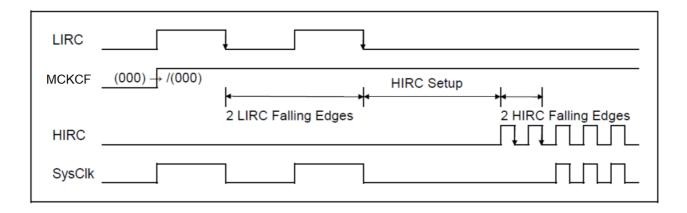

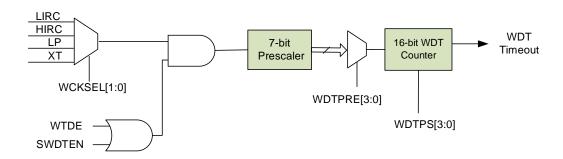

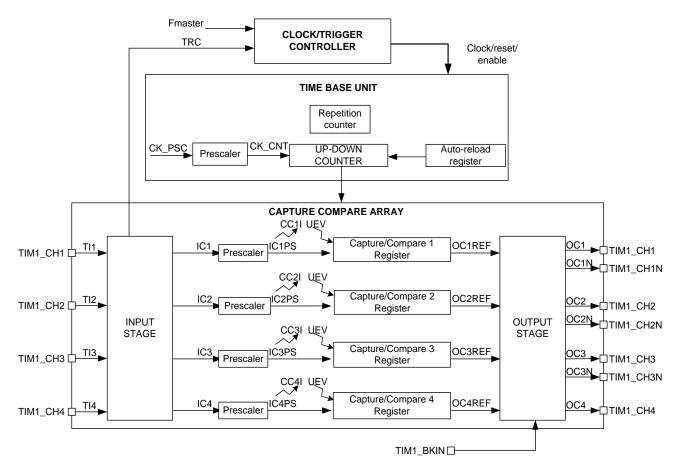

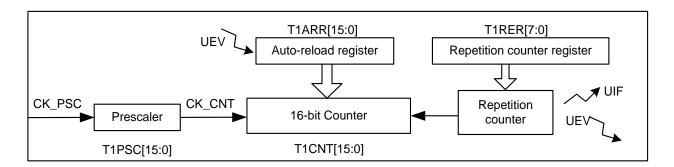

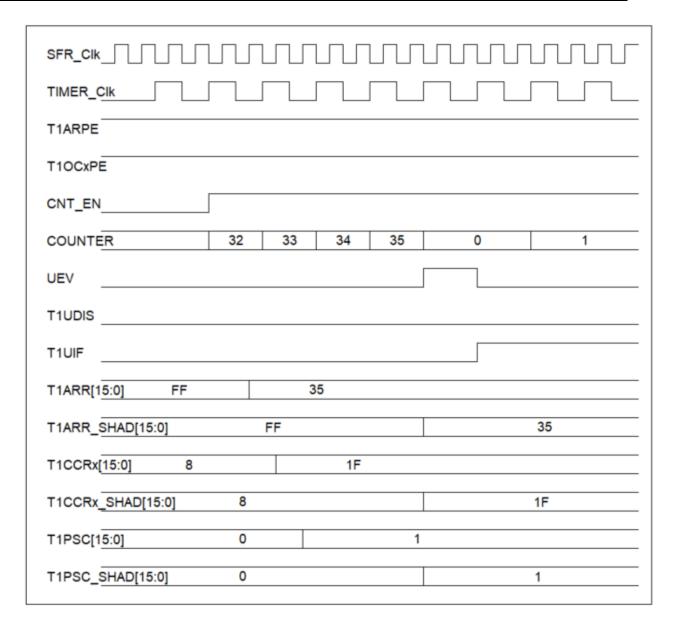

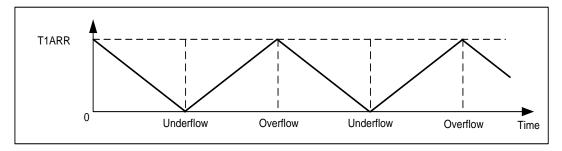

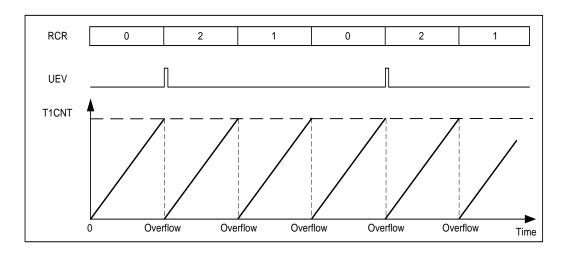

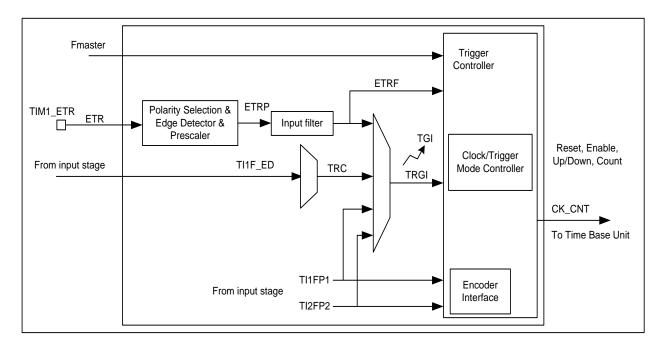

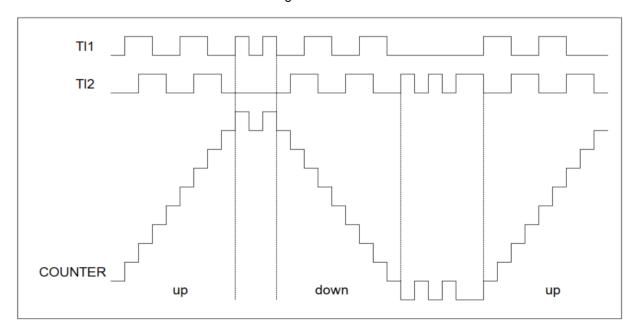

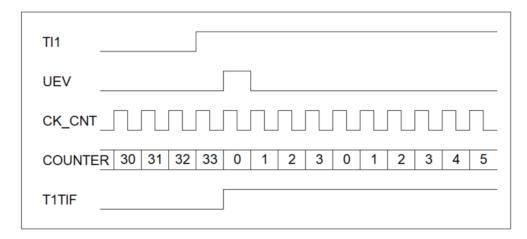

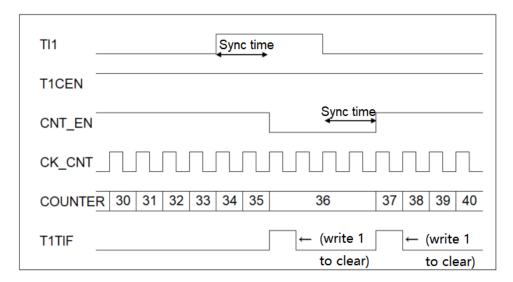

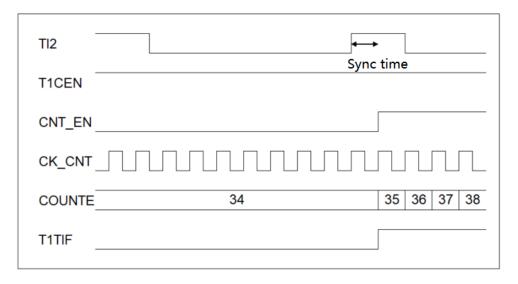

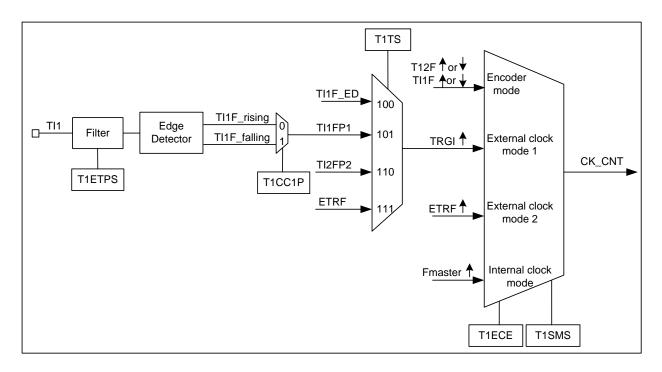

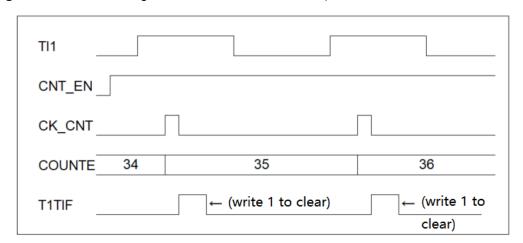

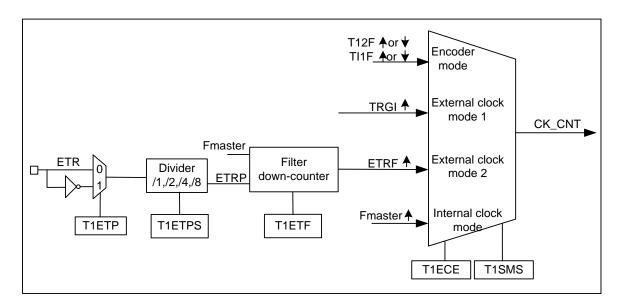

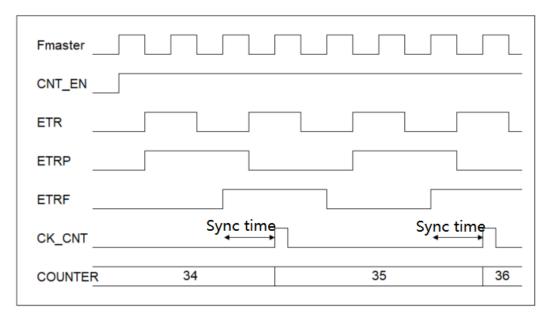

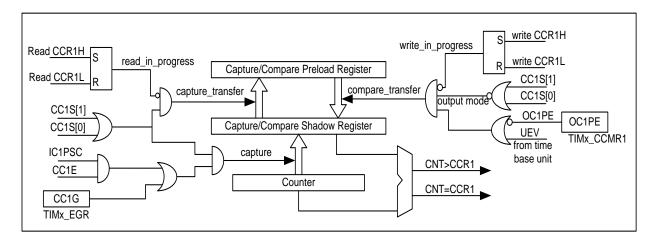

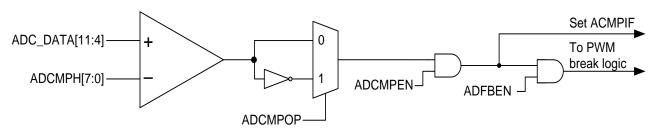

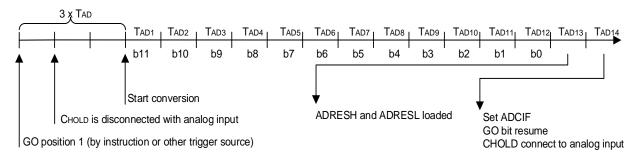

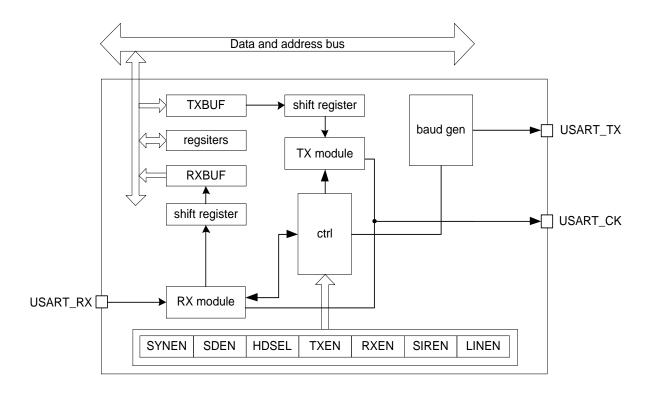

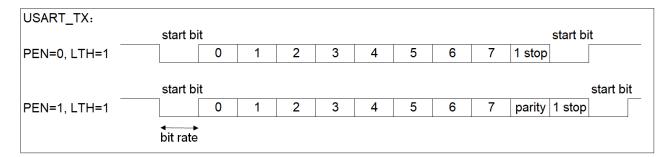

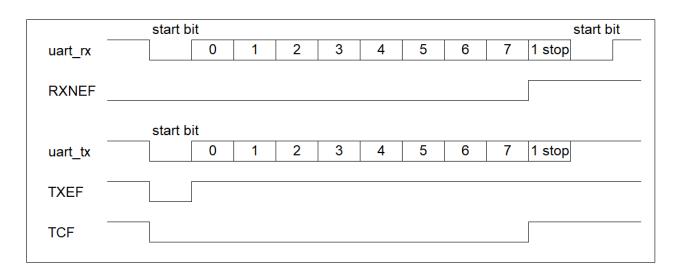

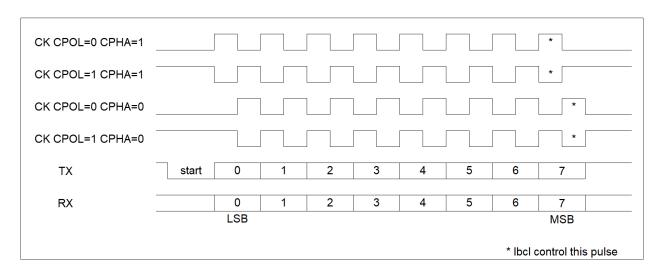

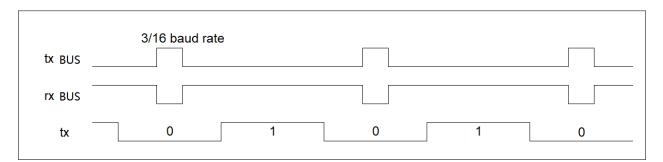

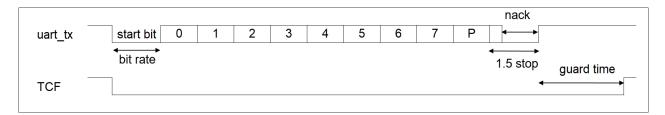

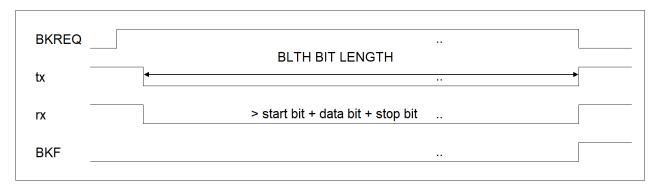

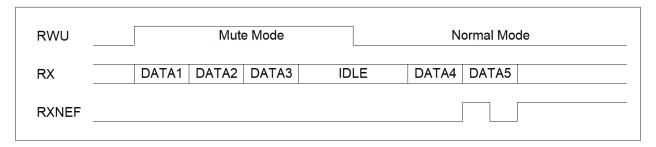

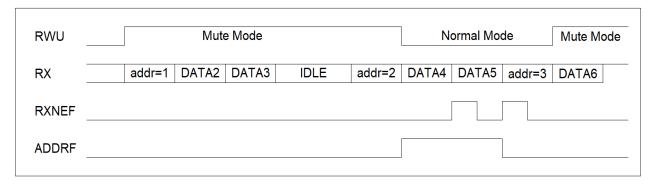

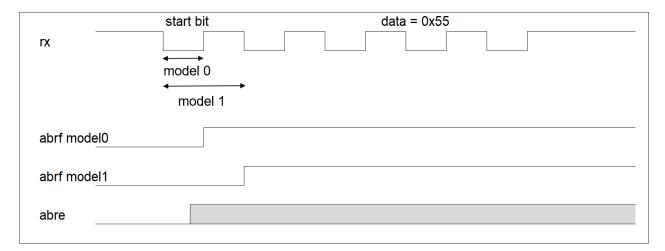

| EMC Reset                                | -       | -       | 1       | -       | -       | -       | -                         | -       | -         | -         |